|

|

PDF ETC5067D Data sheet ( Hoja de datos )

| Número de pieza | ETC5067D | |

| Descripción | POWER AMPLIFIER SERIAL INTERFACE CODEC/FILTERWITH RECEIVE | |

| Fabricantes | STMicroelectronics | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ETC5067D (archivo pdf) en la parte inferior de esta página. Total 18 Páginas | ||

|

No Preview Available !

ETC5064/64-X

ETC5067/67-X

SERIAL INTERFACE CODEC/FILTER WITH RECEIVE

POWER AMPLIFIER

. COMPLETE CODEC AND FILTERING SYS-

TEM INCLUDING :

- Transmit high-pass and low-pass filtering.

- Receive low-pass filter with sin x/x correction.

- Active RC noise filter.

- µ-law or A-law compatible CODER and DE-

CODER.

- Internal precision voltage reference.

- Serial I/O interface.

- Internal auto-zero circuitry.

- Receive push-pull power amplifiers.

. µ-LAW ETC5064

. A-LAW ETC5067

. MEETS OR EXCEEDS ALL D3/D4 AND CCITT

SPECIFICATIONS.

. ± 5 V OPERATION.

. LOW OPERATING POWER-TYPICALLY 70 mW

. POWER-DOWN STANDBY MODE-TYPICALLY

3 mW

. AUTOMATIC POWER DOWN

. TTL OR CMOS COMPATIBLE DIGITAL INTER-

FACES

. MAXIMIZES LINE INTERFACE CARD CIR-

CUIT DENSITY

. 0°C TO 70°C OPERATION: ETC5064/67

. –40°C TO 85°C OPERATION: ETC5064-X/67-X

DIP20

(Plastic) N

ORDERING NUMBERS:

ETC5064N

ETC5064N-X

ETC5067N

ETC5067N-X

PL CC2 0

FN

DESCRIPTION

The ETC5064 (µ-law), ETC5067 (A-law) are mono-

lithic PCM CODEC/FILTERS utilizing the A/D and

D/A conversion architectureshown in the Block Dia-

grams and a serial PCM interface. The devices are

fabricated using double-poly CMOS process.

Similar to the ETC505X family, these devices fea-

ture an additional Receive Power Amplifier to pro-

vide push-pull balanced output drive capability. The

receive gain can be adjusted by means of two ex-

ternal resistors for an output level of up to ± 6.6 V

across a balanced 600Ω load.

Also included is an Analog Loopback switch and

TSX output.

ORDERING NUMBERS:

ETC5064FN

ETC5064FN-X

ETC5067FN

ETC5067FN-X

SO 20

D

ORDERING NUMBERS:

ETC5064D

ETC5064D-X

ETC5067D

ETC5067D-X

November 1994

1/18

1 page

ETC5064 - ETC5064-X - ETC5067 - ETC5067-X

pulses are being used. For 64 kHz operation, the

frame sync pulses must be kept low for a minimum

of 160 ns (see Fig 1). The DX TRI-STATE output

buffer is enabled with the rising edge of FSX or the

rising edge of BCLKX, whichever comes later, and

the first bit clocked out is the sign bit. The following

seven BCLKX rising edges clock out the remaining

seven bits. The DX output is disabled by the falling

BCLKX edge following the eighth rising edge, or by

FSX going low, whichever comes later. A rising edge

on the receive frame sync pulse, FSR, will cause the

PCM data at DR to be latched in on the next eight

falling edges of BCLKR (BCLKx in synchronous

mode). Both devices may utilize the long frame sync

pulse in synchronous or asynchronous mode.

TRANSMIT SECTION

The transmit section input is an operational amplifier

with provision for gain adjustmentusing two external

resistors, see figure 4. The low noiseand wide band-

width allow gains in excess of 20 dB across the

audio passband to be realized. The op amp drives

a unity gain filter consisting of RC active pre-filter,

followed by an eighth order switched-capacitor

bandpass filter directly drives the encoder sample-

and-hold circuit. The A/D is of companding type ac-

cording to A-law (ETC5067 and ETC5067-X) or µ-

law (ETC5064 and ETC5064-X) coding conven-

tions. A precision voltage reference is trimmed in

manufacturing to provide an input over load (tMAX)

of nominally 2.5V peak (see table of Transmission

Characteristics). The FSX frame sync pulse controls

the sampling of the filer output,and then the succes-

sive-approximationencodingcycle begins.The8-bit

code is then loaded into a buffer and shifted out

throughDX at the next FSX pulse. the total encoding

delay will be approximately 165µs (due to the trans-

mit filter) plus 125µs (due to encoding delay), which

totals 290µs. Any offset voltage due to the filters or

comparator is cancelled by sign bit integration.

RECEIVE SECTION

The receive section consist of an expanding DAC

which drives a fifth order switched-capacitor low

pass filter clocked at 256kHz. The decoder is A-law

(ETC5067 and ETC5067-X) or µ–law (ETC5064

and ETC5064-X) and the 5 th order low pass filter

corrects for the sin x/x attenuation due to the 8kHz

sample and hold. The filter is then followed by a 2

nd order RC active post-filter and power amplifier

capable of driving a 600Ω load to a level of 7.2dBm.

The receive section is unity-gain. Upon the oc-

curence of FSR, the data at the DR input is clocked

in on the falling edge of the next eight BCLKR

(BCKLX) periods.At the end ofthe decoder time slot,

the decoding cycle begins, and 10µs later the de-

coder DAC outputis updated.The total decoder de-

lay is about10µs (decoder up-date) plus 110µs (fil-

ter delay) plus 62.5µs (1/2 frame), which gives ap-

proximately 180µs.

RECEIVE POWER AMPLIFIERS

Two inverting mode power amplifiers are provided

for directly driving a matched line interface trans-

former. The gain of the first power amplifier can be

adjusted to boost the ± 2.5V peak output signal from

the receive filter up ± 3.3V peak into an unbalanced

300Ω load, or ±4.0V into an unbalanced15kΩ load.

The second power amplifier is internally connected

in unity-gain inverting mode to give 6dB of signal

gain for balanced loads. Maximum power transfer to

a 600Ω subscriber line termination is obtained by

differientially driving a balanced transformer with a

√2 : 1 turns ratio, as shown in figure 4. A total peak

power of 15.6dBm can be delivered to the load plus

termination. Both power amplifier can be powered

down independentlyfrom the PDN input by connect-

ing the VPI input to VBB saving approximately 12

mW of power.

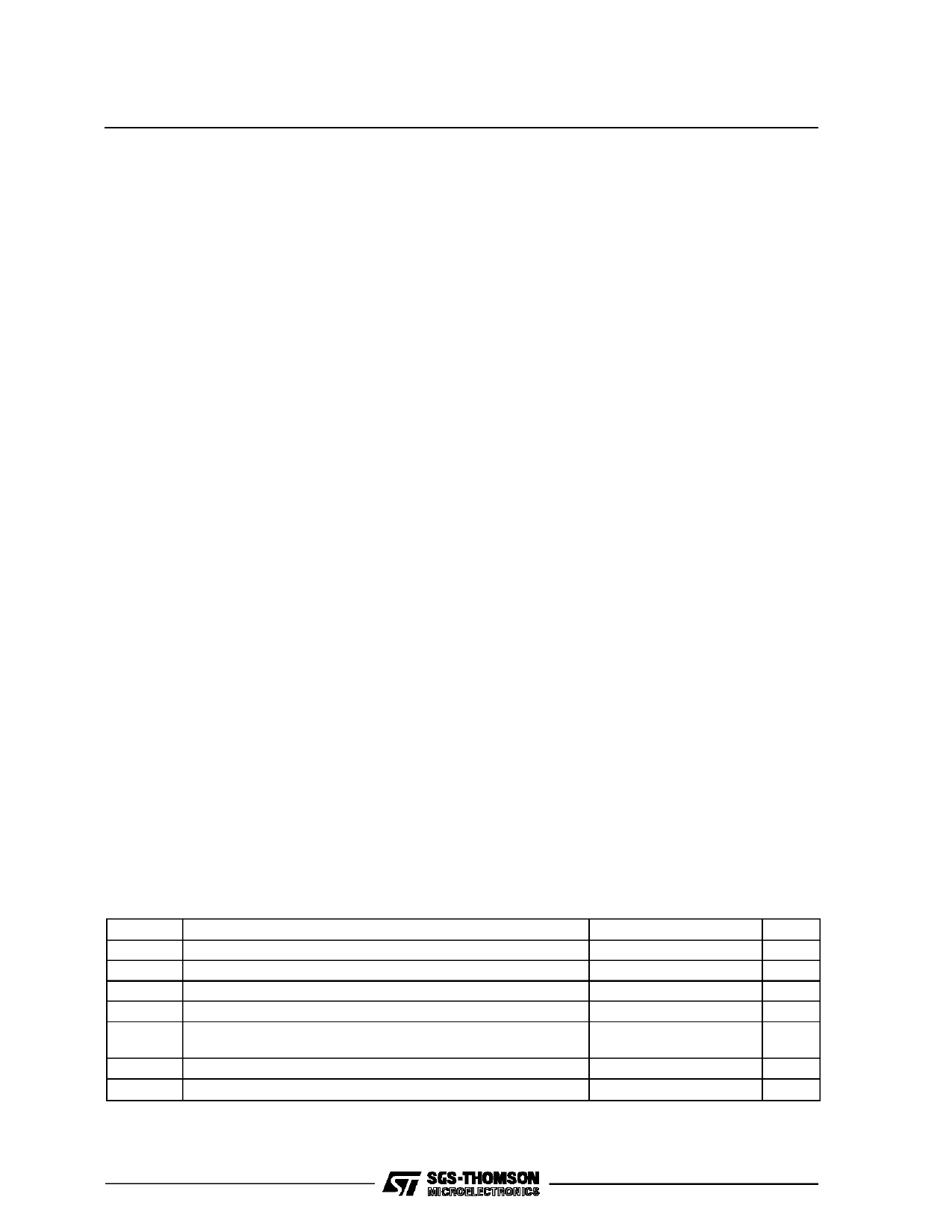

ABSOLUTE MAXIMUM RATINGS

S ym b o l

VCC

VBB

VIN, VOUT

Toper

Tstg

Parameter

VCC to GNDA

VBB to GNDA

Voltage at any Analog Input or Output

Voltage at any Digital Input or Output

Operating Temperature Range: ETC5064/67

ETC5064-X/67-X

Storage Temperature Range

Lead Temperature (soldering, 10 seconds)

Valu e

7

-7

VCC +0.3 to VBB -0.3

VCC +0.3 to GNDA -0.3

-25 to +125

-40 to +125

-65 to +150

300

Unit

V

V

V

V

°C

°C

°C

°C

5/18

5 Page

ETC5064 - ETC5064-X - ETC5067 - ETC5067-X

TRANSMISSION CHARACTERISTICS

(all devices) TA = 0°C to 70°C (ETC5064-X/67-X: TA = –40°C to 85°), VCC = 5V ± 5%, VBB = – 5V ± 5%,

GNDA = 0V, f = 1.02kHz, VIN = 0dBm0 transmit input amplifier connected forunity–gainnon–inverting.(unless

otherwise specified).

AMPLITUDE RESPONSE

Symbo l

tMAX

GXA

GXR

GXAT

GXAV

GXRL

GRA

GRR

GRAT

GRAV

GRRL

VRO

P a ram et er

Absolute Levels - Nominal 0 dBm0 is 4 dBm (600Ω).

0 dBm0

Max Overload Level

3.14 dBm0

3.17 dBm0

ETC5067

ETC5064

Transmit Gain, Absolute (TA = 25°C, VCC = 5V, VBB = -5V)

Input at GSX = 0dBm0 at 1020Hz

Transmit Gain, Relative to GXA

f = 16Hz

f = 50Hz

f = 60Hz

f = 180Hz

f = 200Hz

f = 300Hz -3000Hz

f = 3200Hz (ETC5064-X/67-X)

f = 3300Hz

f = 3400Hz

f = 4000Hz

f = 4600Hz and up, measure response from oHz to 4000Hz

Absolute Transmit Gain Variation with Temperature

TA = 0°C to +70°C

TA = –40°C to +85°C (ETC5064-X/67-X)

Absolute Transmit Gain Variation with Supply Voltage

(VCC = 5V ±5%, VBB = -5V ±5%)

Transmit Gain Variation with Level

Sinusolidal Test Method Reference Level = -10dBm0

VFXI+ = -40dBm0 to +3dBm0

VFXI+ = -50dBm0 to -40dBm0

VFXI+ = -55dBm0 to -50dBm0

Receive Gain, Absolute (TA = 25°C, VCC = 5V, VBB = -5V)

Input = Digital Code Sequence for 0dBm0 Signal at 1020Hz

Receive Gain, Relative to GRA

f = 0Hz to 3000Hz

f = 3200Hz (ETC5064-X/67-X)

f = 3300Hz

f = 3400Hz

f = 4000Hz

Absolute Receive Gain Variation with Temeperature

TA = 0°C to +70°C

TA = –40°C to +85°C (ETC5064-X/67-X)

Absolute Receive Gain Variation with Supply Voltage

(VCC = 5V ±5%, VBB = -5V ±5%)

Receive Gain Variation with Level

Sinusoidal Test Method; Reference Input PCM code

corresponds to an ideally encoded -10dBm0 signal

PCM level = -40dBm0 to +3dBm0

PCM level = -50dBm0 to -40dBm0

PCM level = -55dBm0 to -50dBm0

Receive Filter Output at VFRO RL = 10KΩ

Min. T yp. Max.

1.2276

Unit

Vrms

-0.15

2.492

2.501

0.15

VPK

dB

-

-

-

-2.8

-1.8

-0.15

-0.35

-0.35

-0.7

-0.1

-0.15

-0.05

-40

-30

-26

-0.2

-0.1

0.15 dB

0.20

0.05

0

-14

-32

dB

0.1

0.15

0.05 dB

-0.2

-0.4

-1.2

-0.15

-0.15

-0.35

-0.35

-0.7

-0.1

-0.15

-0.05

0.2

0.4

1.2

0.15

dB

dB

0.15

0.20

0.05

0

-14

0.1

0.15

0.05

dB

dB

dB

-0.2 0.2 dB

-0.4 0.4

-1.2 1.2

-2.5 2.5 V

11/18

11 Page | ||

| Páginas | Total 18 Páginas | |

| PDF Descargar | [ Datasheet ETC5067D.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ETC5067 | POWER AMPLIFIER SERIAL INTERFACE CODEC/FILTERWITH RECEIVE | STMicroelectronics |

| ETC5067-X | POWER AMPLIFIER SERIAL INTERFACE CODEC/FILTERWITH RECEIVE | STMicroelectronics |

| ETC5067D | POWER AMPLIFIER SERIAL INTERFACE CODEC/FILTERWITH RECEIVE | STMicroelectronics |

| ETC5067D-X | POWER AMPLIFIER SERIAL INTERFACE CODEC/FILTERWITH RECEIVE | STMicroelectronics |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |