|

|

PDF HS-3182 Data sheet ( Hoja de datos )

| Número de pieza | HS-3182 | |

| Descripción | ARINC 429 Bus Interface Line Driver Circuit | |

| Fabricantes | Intersil Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de HS-3182 (archivo pdf) en la parte inferior de esta página. Total 7 Páginas | ||

|

No Preview Available !

®

Data Sheet

May 30, 2008

HS-3182

FN2963.3

ARINC 429 Bus Interface Line Driver

Circuit

The HS-3182 is a monolithic dielectric ally isolated bipolar

differential line driver designed to meet the specifications of

ARINC 429. This device is intended to be used with a

companion chip, HS-3282 CMOS ARINC Bus Interface

Circuit, which provides the data formatting and processor

interface function.

All logic inputs are TTL and CMOS compatible. In addition to

the DATA (A) and DATA (B) inputs, there are also inputs for

CLOCK and SYNC signals which are AND’d with the DATA

inputs. This feature enhances system performance and

allows the HS-3182 to be used with devices other than the

HS-3182.

Three power supplies are necessary to operate the HS-3182:

+V = +15V ±10%, -V = -15V ±10%, and V1 = 5V ±5%. VREF is

used to program the differential output voltage swing such that

VOUT (DIFF) = ±2VREF. Typically, VREF = V1 = 5V ±5%, but a

separate power supply may be used for VREF which should

not exceed 6V.

The driver output impedance is 75Ω ±20% at +25°C. Driver

output rise and fall times are independently programmed

through the use of two external capacitors connected to the CA

and CB inputs. Typical capacitor values are CA = CB = 75pF for

high-speed operation (100kBPS), and CA = CB = 300pF for

low-speed operation (12kBPS to 14.5kBPS). The outputs are

protected against overvoltage and short circuit as shown in the

Block Diagram. The HS-3182 is designed to operate over an

ambient temperature range of -55°C to +125°C, or -40°C to

+85°C.

TABLE 1. TRUTH TABLE

SYNC CLK DATA (A) DATA (B) AOUT BOUT COMMENTS

XL

X

X 0V 0V

Null

LX

X

X 0V 0V

Null

HH

L

L 0V 0V

Null

HH

HH

HH

L

H

H

H -VREF +VREF

L +VREF -VREF

H 0V 0V

Low

High

Null

Features

• RoHS/Pb-free Available for SBDIP Package (100% Gold

Termination Finish)

• TTL and CMOS Compatible Inputs

• Adjustable Rise and Fall Times via Two External

Capacitors

• Programmable Output Differential Voltage via VREF Input

• Operates at Data Rates Up to 100k Bits/s

• Output Short Circuit Proof and Contains Overvoltage

Protection

• Outputs are Inhibited (0V) If DATA (A) and DATA (B)

Inputs are Both in the “Logic One” State

• DATA (A) and DATA (B) Signals are “AND’d” with Clock

and Sync Signals

• Full Military Temperature Range

Pinouts

HS-3182

(16 LD SBDIP)

TOP VIEW

VREF 1

GND 2

SYNC 3

DATA (A) 4

CA

AOUT

-V

5

6

7

GND 8

16 V1

15 NC

14 CLK

13 DATA (B)

12 CB

11 BOUT

10 NC

9 +V

HS-3182

(28 LD CLCC)

TOP VIEW

4 3 2 1 28 27 26

NC 5

25 CLK

DATA (A) 6

24 NC

NC 7

23 DATA (B)

NC 8

22 CB

CA 9

21 NC

NC 10

20 NC

NC 11

19 NC

12 13 14 15 16 17 18

1 CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 1-888-468-3774 | Intersil (and design) is a registered trademark of Intersil Americas Inc.

Copyright Intersil Americas Inc. 1997, 2007, 2008. All Rights Reserved

All other trademarks mentioned are the property of their respective owners.

1 page

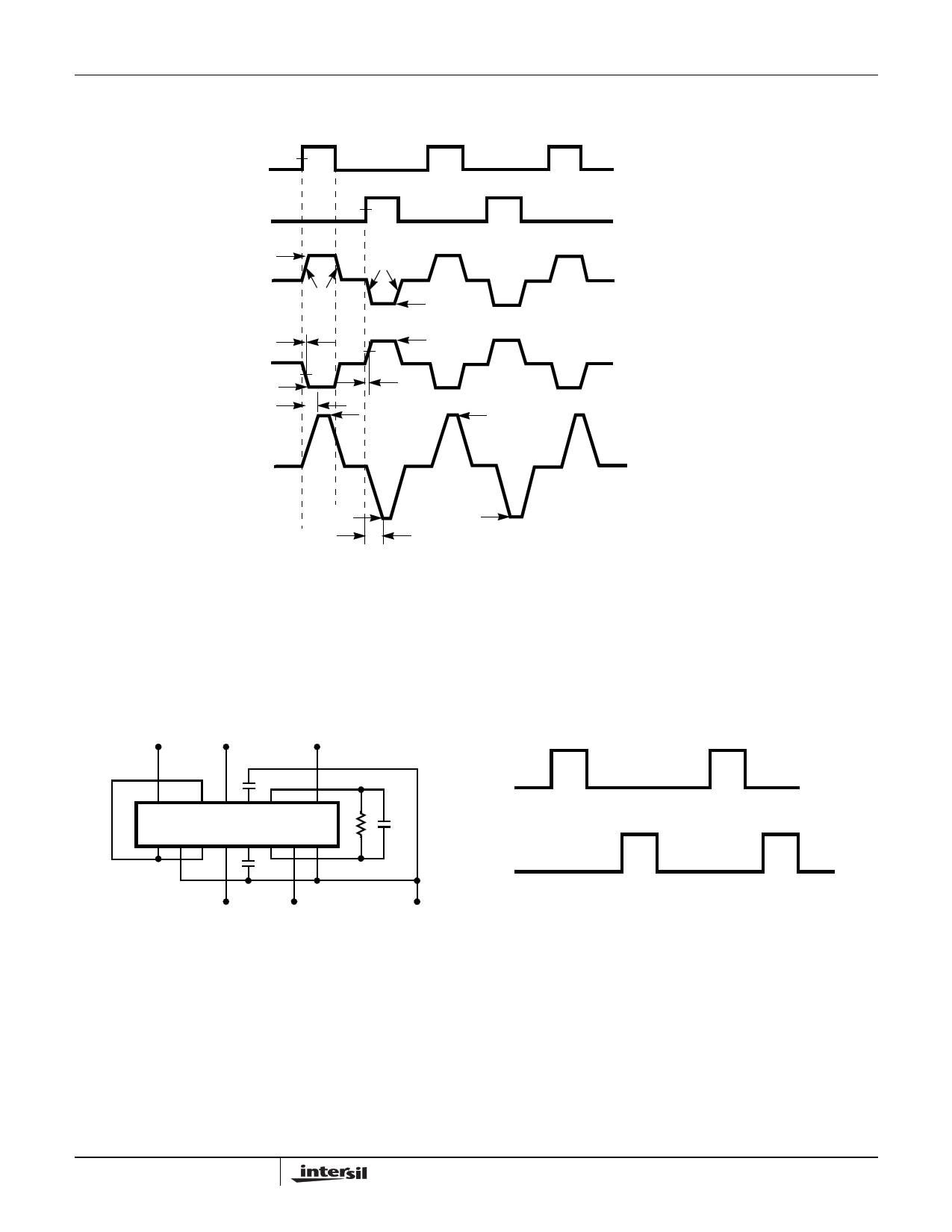

Driver Waveforms

HS-3182

50%

DATA (A) 0V

5V

0V

DATA (B) 0V

50%

5V

0V

VREF

AOUT 0V

ADJ. BY

CB

ADJ. BY

CA

-VREF

tPHL

BOUT 0V

50%

-VREF

tR

50%

VREF

tPLH

2VREF

HIGH

+4.75V TO +5.25V

-4.75V TO -5.25V

+4.75V TO +5.25V

-4.75V TO -5.25V

+9.5V TO +10.5V

DIFFERENTIAL AOUT - BOUT

OUTPUT 0V

NULL

-2VREF

NOTES:

tR measured 50% to 90% x 2

tF measured 50% to 10% x 2

VIH = 5V VOL = -4.75V to -5.25V

VIL = 0V VOH = 4.75V to 5.25V

tF

LOW

NOTE: OUTPUTS UNLOADED

-9.5V TO -10.5V

When the Data (A) input is in the Logic One state and the Data (B)

input is in the Logic Zero state, AOUT is equal to VREF and BOUT is

equal to -VREF. This constitutes the Output High state. Data (A) and

Data (B) both in the Logic Zero state causes both AOUT and BOUT

to be equal to 0V which designates the output Null state. Data (A) in

the Logic Zero state and Data (B) in the Logic One state causes

AOUT to be equal to -VREF and BOUT to be equal to VREF which is

the Output Low state.

Burn-In Schematic

V1 DATA (B)

+V

C3

16 15 14 13 12 11 10 9

HS-3182

1 2 3 4 5 6 78

R

C2

C1

A

B

VIH

VIL

VIH

VIL

DATA (A)

-V

GND

NOTES:

R = 400Ω ± 5%

C1 = 0.03mF ± 20%

C2 = C3 = 500pF, NPO

+V = +15.5V ± 0.5V

-V = -15.5V ± 0.5V

V1 = +5.5V ± 0.5V

A 0.0mF decoupling capacitor is required on each of the three

supply lines (+V, -V and V1) at every 3rd Burn-In socket.

Ambient Temp. Max. = +125°C.

Package = 16 Lead Side Brazed DIP.

Pulse Conditions = A & B = 6.25kHz ±10%. B is delayed one-half

cycle and in sync with A.

VIH = 2.0V Min.

VIL = 0.5V Max.

5 FN2963.3

May 30, 2008

5 Page | ||

| Páginas | Total 7 Páginas | |

| PDF Descargar | [ Datasheet HS-3182.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| HS-3182 | ARINC 429 Bus Interface Line Driver Circuit | Intersil Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |