|

|

PDF HYB3117400BJ-50 Data sheet ( Hoja de datos )

| Número de pieza | HYB3117400BJ-50 | |

| Descripción | 4M x 4-Bit Dynamic RAM 2k & 4k Refresh | |

| Fabricantes | Siemens Semiconductor Group | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de HYB3117400BJ-50 (archivo pdf) en la parte inferior de esta página. Total 26 Páginas | ||

|

No Preview Available !

3.3V 4M x 4-Bit Dynamic RAM

HYB3116400BJ/BT(L) -50/-60/-70

HYB3117400BJ/BT(L) -50/-60/-70

Advanced Information

• 4 194 304 words by 4-bit organization

• 0 to 70 °C operating temperature

• Performance:

tRAC

tCAC

tAA

tRC

tPC

RAS access time

CAS access time

Access time from address

Read/Write cycle time

Fast page mode cycle time

-50 -60 -70

50 60 70 ns

13 15 20 ns

25 30 35 ns

90 110 130 ns

35 40 45 ns

• Single + 3.3 V (± 0.3V ) supply

• Low power dissipation

max. 396 active mW (HYB3117400BJ/BT-50)

max. 363 active mW (HYB3117400BJ/BT-60)

max. 330 active mW (HYB3117400BJ/BT-70)

max. 360 active mW (HYB3116400BJ/BT-50)

max. 324 active mW (HYB3116400BJ/BT-60)

max. 288 active mW (HYB3116400BJ/BT-70)

7.2 mW standby (LV-TTL)

3.6 mW standby (LV-CMOS)

720 µW standby for L-version

• Output unlatched at cycle end allows two-dimensional chip selection

• Read, write, read-modify-write, CAS-before-RAS refresh, RAS-only refresh, hidden refresh,

Self Refresh and test mode

• Fast page mode capability

• All inputs, outputs and clocks fully TTL-compatible

• 2048 refresh cycles / 32 ms for HYB3117400

4096 refresh cycles / 64 ms for HYB3116400

• Plastic Package:

P-SOJ-26/24-1 (300 mil)

P-TSOPII-26/24-1 (300mil)

Semiconductor Group

1

1.96

1 page

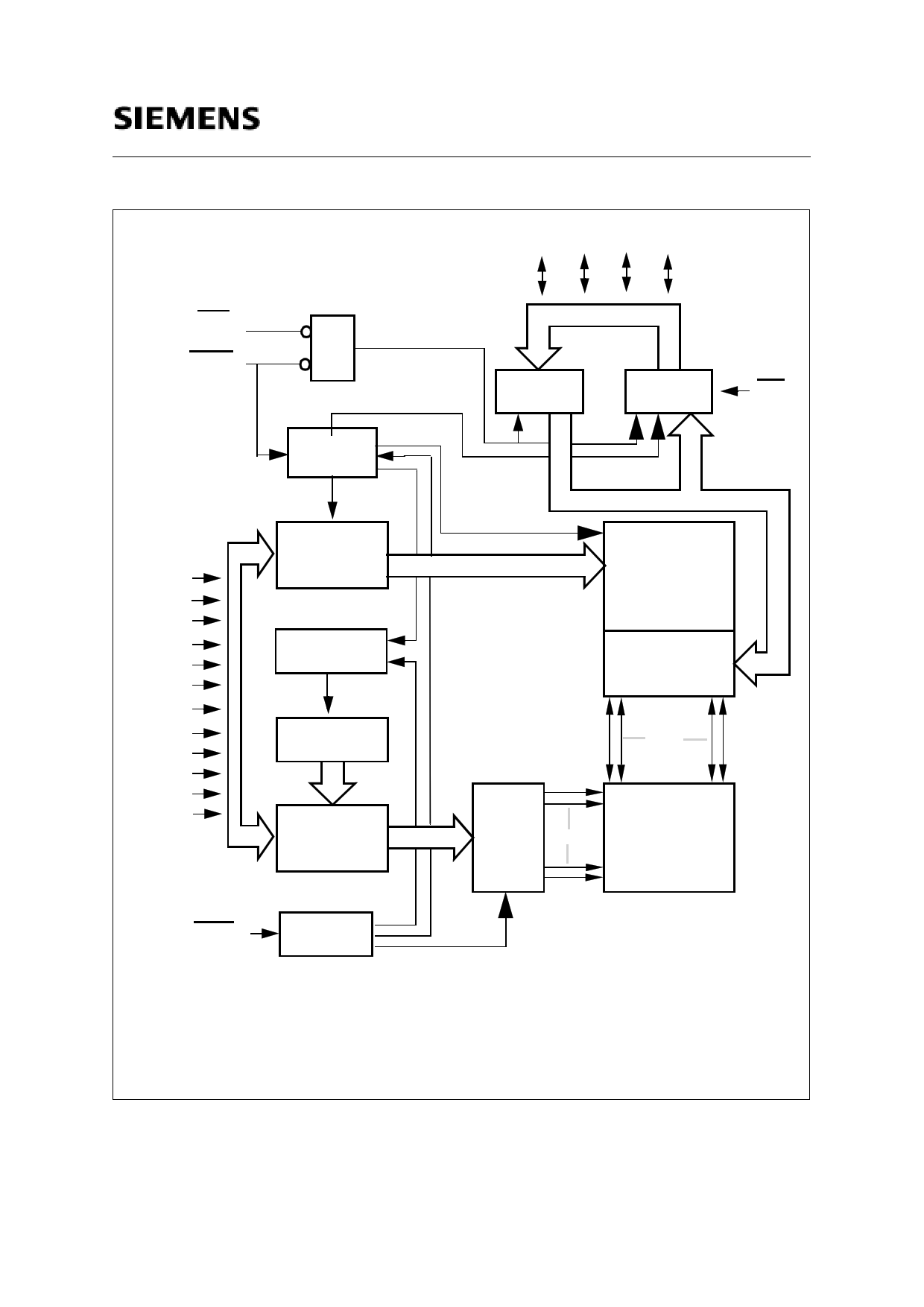

HYB 3116(7)400BJ/BT(L) -50/-60/-70

3.3V 4Mx4-DRAM

I/O1 I/O2 I/O3 I/O4

WE

.CAS

&

No. 2 Clock

Generator

Data in

Buffer

4

Data out

Buffer

4

OE

Column

10 Address

A0 Buffer(10)

A1

10 Column

Decoder

A2

A3 Refresh

A4 Controller

A5

Sense Amplifier

I/O Gating

4

A6

A7 Refresh

A8 Counter (12)

A9

A10 12

1024

x4

A11 Row

Row

Memory Array

12 Address

Buffers(12)

12 Decoder 4096 4096x1024x4

RAS

No. 1 Clock

Generator

Block Diagram for HYB3116400

Semiconductor Group

5

5 Page

HYB 3116(7)400BJ/BT(L) -50/-60/-70

3.3V 4Mx4-DRAM

Notes:

1) All voltages are referenced to VSS.

2) ICC1, ICC3, ICC4 and ICC6 depend on cycle rate.

3) ICC1 and ICC4 depend on output loading. Specified values are measured with the output open.

4) Address can be changed once or less while RAS = VIL. In the case of ICC4 it can be changed once or less

during a fast page mode cycle (tPC).

5) An initial pause of 200 µs is required after power-up followed by 8 RAS cycles of which at least one cycle has

to be a refresh cycle, before proper device operation is achieved. In case of using internal refresh counter, a

minimum of 8 CAS-before-RAS initialization cycles instead of 8 RAS cycles are required.

6) AC measurements assume tT = 5 ns.

7) VIH (min.) and VIL (max.) are reference levels for measuring timing of input signals. Transition times are also

measured between VIH and VIL.

8) Measured with a load equivalent to 100 pF and at Voh=2.0 V (Ioh = -2mA) , Vol=0.8V (Iol=2mA).

9) Operation within the tRCD (max.) limit ensures that tRAC (max.) can be met. tRCD (max.) is specified as a

reference point only: If tRCD is greater than the specified tRCD (max.) limit, then access time is controlled by

tCAC.

10)Operation within the tRAD (max.) limit ensures that tRAC (max.) can be met. tRAD (max.) is specified as a

reference point only: If tRAD is greater than the specified tRAD (max.) limit, then access time is controlled by

tAA.

11)Either tRCH or tRRH must be satisfied for a read cycle.

12)tOFF (max.) and tOEZ (max.) define the time at which the outputs achieve the open-circuit condition and are

not referenced to output voltage levels.

13)Either tDZC or tDZO must be satisfied.

14)Either tCDD or tODD must be satisfied.

15)tWCS, tRWD, tCWD, tAWD and tCPWD are not restrictive operating parameters. They are included in the data

sheet as electrical characteristics only. If tWCS > tWCS (min.), the cycle is an early write cycle and the I/O pin

will remain open-circuit (high impedance) through the entire cycle; if tRWD > tRWD (min.), tCWD > tCWD

(min.), tAWD > tAWD (min.) and tCPWD > tCPWD (min.) , the cycle is a read-write cycle and I/O pins will

contain data read from the selected cells. If neither of the above sets of conditions is satisfied, the condition of

the I/O pins (at access time) is indeterminate.

16)These parameters are referenced to the CAS leading edge in early write cycles and to the WE leading edge

in read-write cycles.

17)When using Self Refresh mode, the following refresh operations must be performed to ensure proper DRAM

operation:

If row addresses are being refreshed on an evenly distributed manner over the refresh interval using CBR

refresh cycles, then only one CBR cycle must be performed immediately after exit from Self Refresh.

If row addresses are being refreshed in any other manner (ROR - Distributed/Burst; or CBR-Burst) over the

refresh interval, then a full set of row refreshes must be performed immediately before entry to and immediately

after exit from Self Refresh.

Semiconductor Group

11

11 Page | ||

| Páginas | Total 26 Páginas | |

| PDF Descargar | [ Datasheet HYB3117400BJ-50.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| HYB3117400BJ-50 | 3.3V 4M x 4-Bit Dynamic RAM | Siemens Semiconductor Group |

| HYB3117400BJ-50 | 4M x 4-Bit Dynamic RAM 2k & 4k Refresh | Siemens Semiconductor Group |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |