|

|

PDF M28W800BT Data sheet ( Hoja de datos )

| Número de pieza | M28W800BT | |

| Descripción | 8 Mbit 3V Supply Flash Memory | |

| Fabricantes | STMicroelectronics | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de M28W800BT (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

M28W800BT

M28W800BB

8 Mbit (512Kb x16, Boot Block)

3V Supply Flash Memory

FEATURES SUMMARY

s SUPPLY VOLTAGE

– VDD = 2.7V to 3.6V Core Power Supply

– VDDQ= 1.65V to 3.6V for Input/Output

– VPP = 12V for fast Program (optional)

s ACCESS TIME: 70, 85, 90,100ns

s PROGRAMMING TIME

– 10µs typical

– Double Word Programming Option

s COMMON FLASH INTERFACE

– 64 bit Security Code

s MEMORY BLOCKS

– Parameter Blocks (Top or Bottom location)

– Main Blocks

s BLOCK PROTECTION on TWO PARAMETER

BLOCKS

– WP for Block Protection

s AUTOMATIC STAND-BY MODE

s PROGRAM and ERASE SUSPEND

s 100,000 PROGRAM/ERASE CYCLES per

BLOCK

s ELECTRONIC SIGNATURE

– Manufacturer Code: 20h

– Top Device Code, M28W800BT: 8892h

– Bottom Device Code, M28W800BB: 8893h

Figure 1. Packages

FBGA

TFBGA46 (ZB)

6.39 x 6.37mm

TSOP48 (N)

12 x 20mm

May 2002

1/42

1 page

M28W800BT, M28W800BB

SUMMARY DESCRIPTION

The M28W800B is a 8 Mbit (512Kbit x 16) non-vol-

atile Flash memory that can be erased electrically

at the block level and programmed in-system on a

Word-by-Word basis. These operations can be

performed using a single low voltage (2.7 to 3.6V)

supply. VDDQ allows to drive the I/O pin down to

1.65V. An optional 12V VPP power supply is pro-

vided to speed up customer programming.

The device features an asymmetrical blocked ar-

chitecture. The M28W800B has an array of 23

blocks: 8 Parameter Blocks of 4 KWord and 15

Main Blocks of 32 KWord. M28W800BT has the

Parameter Blocks at the top of the memory ad-

dress space while the M28W800BB locates the

Parameter Blocks starting from the bottom. The

memory maps are shown in Figure 5, Block Ad-

dresses.

Parameter blocks 0 and 1 can be protected from

accidental programming or erasure. Each block

can be erased separately. Erase can be suspend-

ed in order to perform either read or program in

any other block and then resumed. Program can

be suspended to read data in any other block and

then resumed. Each block can be programmed

and erased over 100,000 cycles.

Program and Erase commands are written to the

Command Interface of the memory. An on-chip

Program/Erase Controller takes care of the tim-

ings necessary for program and erase operations.

The end of a program or erase operation can be

detected and any error conditions identified. The

command set required to control the memory is

consistent with JEDEC standards.

The memory is offered in TSOP48 (10 X 20mm),

and TFBGA46 (6.39 x 6.37mm, 0.75mm pitch)

packages and is supplied with all the bits erased

(set to ’1’).

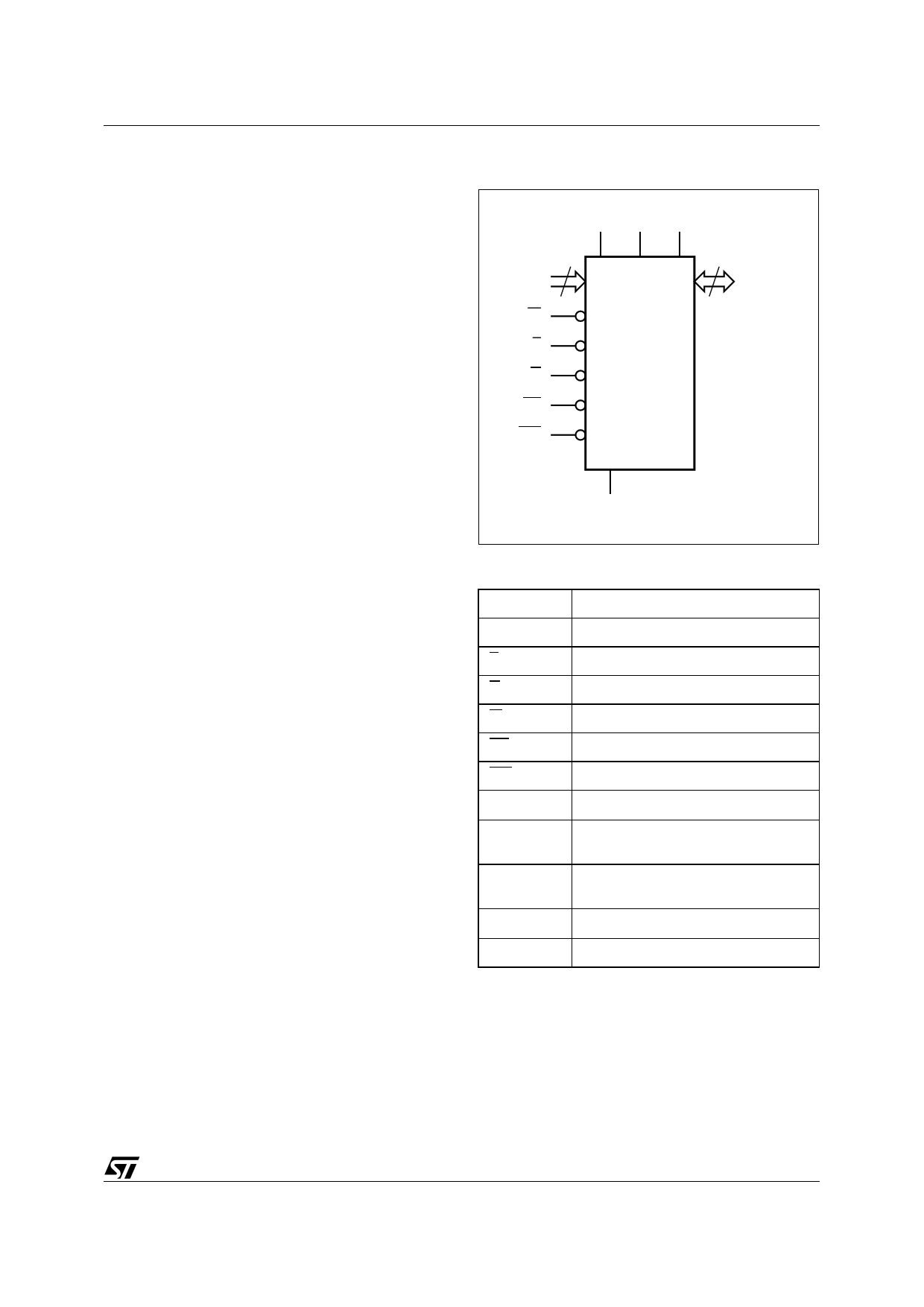

Figure 2. Logic Diagram

VDD VDDQ VPP

19

A0-A18

W

E

G

RP

WP

16

DQ0-DQ15

M28W800BT

M28W800BB

VSS

AI03581

Table 1. Signal Names

A0-A18

Address Inputs

DQ0-DQ15 Data Input/Output

E Chip Enable

G Output Enable

W Write Enable

RP Reset

WP Write Protect

VDD Core Power Supply

VDDQ

Power Supply for

Input/Output

VPP

Optional Supply Voltage for

Fast Program & Erase

VSS Ground

NC Not Connected Internally

5/42

5 Page

M28W800BT, M28W800BB

COMMAND INTERFACE

All Bus Write operations to the memory are inter-

preted by the Command Interface. Commands

consist of one or more sequential Bus Write oper-

ations. An internal Program/Erase Controller han-

dles all timings and verifies the correct execution

of the Program and Erase commands. The Pro-

gram/Erase Controller provides a Status Register

whose output may be read at any time, to monitor

the progress of an operation, or the Program/

Erase states. See Appendix D, Table 29, Write

State Machine Current/Next, for a summary of the

Command Interface.

The Command Interface is reset to Read mode

when power is first applied, when exiting from Re-

set or whenever VDD is lower than VLKO. Com-

mand sequences must be followed exactly. Any

invalid combination of commands will reset the de-

vice to Read mode. Refer to Table 3, Commands,

in conjunction with the text descriptions below.

Read Memory Array command

The Read command returns the memory to its

Read mode. One Bus Write cycle is required to is-

sue the Read Memory Array command and return

the memory to Read mode. Subsequent read op-

erations will read the addressed location and out-

put the data. When a device Reset occurs, the

memory defaults to Read mode.

Read Status Register Command

The Status Register indicates when a program or

erase operation is complete and the success or

failure of the operation itself. Issue a Read Status

Register command to read the Status Register’s

contents. Subsequent Bus Read operations read

the Status Register, at any address, until another

command is issued. See Table 7, Status Register

Bits, for details on the definitions of the bits.

The Read Status Register command may be is-

sued at any time, even during a Program/Erase

operation. Any Read attempt during a Program/

Erase operation will automatically output the con-

tent of the Status Register.

Read Electronic Signature Command

The Read Electronic Signature command reads

the Manufacturer and Device Codes.

The Read Electronic Signature command consists

of one write cycle, a subsequent read will output

the Manufacturer or the Device Code depending

on the levels of A0. The Manufacturer Code is out-

put when the address line A0 is at VIL, the Device

Code is output when A0 is at VIH. Addresses A1-

A7 must be kept to VIL, other addresses are ig-

nored. The codes are output on DQ0-DQ7 with

DQ8-DQ15 at 00h. (see Table 4)

Read CFI Query Command

The Read Query Command is used to read data

from the Common Flash Interface (CFI) Memory

Area, allowing programming equipment or appli-

cations to automatically match their interface to

the characteristics of the device.

One Bus Write cycle is required to issue the Read

Query Command. Once the command is issued

subsequent Bus Read operations read from the

Common Flash Interface Memory Area. See Ap-

pendix B, Common Flash Interface, Tables 23, 24,

25, 26, 27 and 28 for details on the information

contained in the Common Flash Interface memory

area.

Block Erase Command

The Block Erase command can be used to erase

a block. It sets all the bits within the selected block

to ’1’. All previous data in the block is lost. If the

block is protected then the Erase operation will

abort, the data in the block will not be changed and

the Status Register will output the error.

Two Bus Write cycles are required to issue the

command.

s The first bus cycle sets up the Erase command.

s The second latches the block address in the

internal state machine and starts the Program/

Erase Controller.

If the second bus cycle is not Write Erase Confirm

(D0h), Status Register bits b4 and b5 are set and

the command aborts.

Erase aborts if Reset turns to VIL. As data integrity

cannot be guaranteed when the Erase operation is

aborted, the block must be erased again.

During Erase operations the memory will only ac-

cept the Read Status Register command and the

Program/Erase Suspend command, all other com-

mands will be ignored. Typical Erase times are

given in Table 6, Program, Erase Times and Pro-

gram/Erase Endurance Cycles.

See Appendix C, Figure 19, Erase Flowchart and

Pseudo Code, for the flowchart for using the Erase

command.

Program Command

The memory array can be programmed word-by-

word. Two bus write cycles are required to issue

the Program command.

s The first bus cycle sets up the Program

command.

s The second latches the Address and the Data to

be written and starts the Program/Erase

Controller.

During Program operations the memory will only

accept the Read Status Register command and

the Program/Erase Suspend command. All other

11/42

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet M28W800BT.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| M28W800BB | 8 Mbit 3V Supply Flash Memory | STMicroelectronics |

| M28W800BT | 8 Mbit 3V Supply Flash Memory | STMicroelectronics |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |