|

|

PDF ISL76161 Data sheet ( Hoja de datos )

| Número de pieza | ISL76161 | |

| Descripción | High Speed D/A Converter | |

| Fabricantes | Intersil | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ISL76161 (archivo pdf) en la parte inferior de esta página. Total 12 Páginas | ||

|

No Preview Available !

Data Sheet

December 23, 2013

ISL76161

FN6720.2

12-Bit, +3.3V, 130MSPS, High Speed D/A

Converter

The ISL76161 is a 12-bit, 130MSPS (Mega-Samples Per

Second), CMOS, high speed, low power, D/A (digital to

analog) converter, designed specifically for use in radar

systems or high performance communication systems, such

as base transceiver stations utilizing 2.5G or 3G cellular

protocols.

Pinout

ISL76161

(28 LD TSSOP)

TOP VIEW

D11 (MSB) 1

D10 2

D9 3

D8 4

D7 5

D6 6

D5 7

D4 8

D3 9

D2 10

D1 11

D0 (LSB) 12

DCOM 13

DCOM 14

28 CLK

27 DVDD

26 DCOM

25 NC

24 AVDD

23 COMP

22 IOUTA

21 IOUTB

20 ACOM

19 NC

18 FSADJ

17 REFIO

16 REFLO

15 SLEEP

Features

• High Speed. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130MSPS

• Low Power . . . . . 103mW with 20mA Output at 130MSPS

• Adjustable Full Scale Output Current . . . . . 2mA to 20mA

• Excellent Spurious Free Dynamic Range

(73dBc to Nyquist, fS = 130MSPS, fOUT = 10MHz)

• Automotive Qualified Component

• Extended Temperature Operation: -40°C to +105°C

• +3.3V Power Supply

• 3V LVCMOS Compatible Inputs

• UMTS Adjacent Channel Power = 70dB at 19.2MHz

• EDGE/GSM SFDR = 90dBc at 11MHz in 20MHz Window

• Pb-Free (RoHS Compliant)

Applications

• Automotive Radar Systems

- 24GHz and 77GHz Radar for Adaptive Cruise Control

• Cellular Infrastructure - Single or Multi-Carrier: IS-136,

IS-95, GSM, EDGE, CDMA2000, WCDMA, TDS-CDMA

• Wireless Communication Systems

• High Resolution Imaging Systems

• Arbitrary Waveform Generators

Ordering Information

PART NUMBER

(Note 1)

PART MARKING

CLOCK SPEED

TEMP. RANGE

(°C)

PACKAGE

(Pb-Free, Note 2)

PKG. DWG. #

ISL76161AVZ

ISL76161 AVZ

130MHz

-40 to +105

28 Ld TSSOP

M28.173

ISL76161AVZ-T*

ISL76161 AVZ

130MHz

-40 to +105

28 Ld TSSOP Tape and Reel M28.173

ISL76161AVZ-TK*

ISL76161 AVZ

130MHz

-40 to +105

28 Ld TSSOP Tape and Reel M28.173

*Please refer to TB347 for details on reel specifications.

NOTES:

1. These parts have been qualified in accordance with AEC-Q100 rev F recommendations, some exceptions may apply. Request qualification plan

for further details.

2. These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100%

matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations).

Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC

J STD-020.

1

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 1-888-468-3774 | Copyright Intersil Americas LLC 2008, 2013. All Rights Reserved

Intersil (and design) is a trademark owned by Intersil Corporation or one of its subsidiaries.

All other trademarks mentioned are the property of their respective owners.

1 page

ISL76161

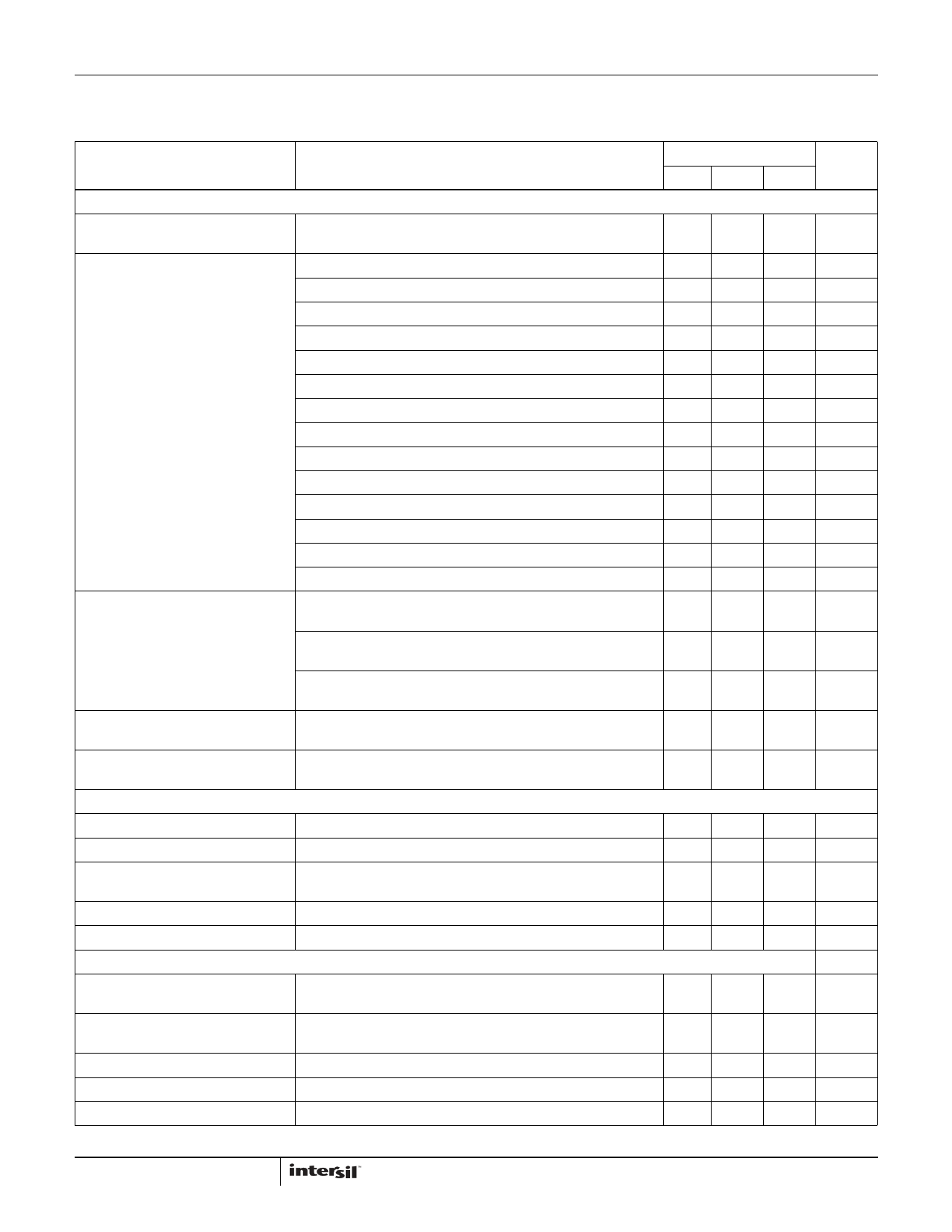

Electrical Specifications

AVDD = DVDD = +3.3V, VREF = Internal 1.2V, IOUTFS = 20mA, TA = +25°C for All Typical Values; Parameters

with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established

by characterization and are not production tested. (Continued)

PARAMETER

TEST CONDITIONS

TA = -40°C TO +105°C

MIN TYP MAX

UNITS

AC CHARACTERISTICS (Using Figure 12 with RDIFF = 100, RLOAD = RA = RB = 50, Full Scale Output = -2.0dBm

Spurious Free Dynamic Range,

SFDR Within a Window

fCLK = 130MSPS, fOUT = 20.2MHz, 20MHz Span (Notes 6, 8)

- 85 - dBc

Spurious Free Dynamic Range,

SFDR to Nyquist (fCLK/2)

fCLK = 130MSPS, fOUT = 50.5MHz (Notes 6, 8)

fCLK = 130MSPS, fOUT = 40.4MHz (Notes 6, 8)

- 57 - dBc

- 62 - dBc

fCLK = 130MSPS, fOUT = 20.2MHz (Notes 6, 9)

- 69 - dBc

fCLK = 130MSPS, fOUT = 10.1MHz (Notes 6, 8)

- 73 - dBc

fCLK = 130MSPS, fOUT = 5.05MHz, T = +25°C (Notes 6, 8)

70 77 - dBc

fCLK = 130MSPS, fOUT = 5.05MHz, T = -40°C to +105°C (Notes 6, 8) 67

-

- dBc

fCLK = 100MSPS, fOUT = 40.4MHz (Notes 6, 8)

- 60 - dBc

fCLK = 80MSPS, fOUT = 30.3MHz (Notes 6, 8)

- 63 - dBc

fCLK = 80MSPS, fOUT = 20.2MHz (Notes 6, 8)

- 69 - dBc

fCLK = 80MSPS, fOUT = 10.1MHz (Notes 6, 8, 10)

- 70 - dBc

fCLK = 80MSPS, fOUT = 5.05MHz (Notes 6, 8)

- 76 - dBc

fCLK = 50MSPS, fOUT = 20.2MHz (Notes 6, 8)

- 68 - dBc

fCLK = 50MSPS, fOUT = 10.1MHz (Notes 6, 8)

- 73 - dBc

fCLK = 50MSPS, fOUT = 5.05MHz (Notes 6, 8)

- 77 - dBc

Spurious Free Dynamic Range,

fCLK = 130MSPS, fOUT = 17.5MHz to 27.9MHz, 1.3MHz Spacing,

-

68

-

dBc

SFDR in a Window with Eight Tones 35MHz Span (Notes 6, 8)

fCLK = 80MSPS, fOUT = 10.8MHz to 17.2MHz, 811kHz Spacing, - 75 - dBc

15MHz Span (Notes 6, 8)

fCLK = 50MSPS, fOUT = 6.7MHz to 10.8MHz, 490kHz Spacing,

10MHz Span (Notes 6, 8)

- 77 - dBc

Spurious Free Dynamic Range,

fCLK = 78MSPS, fOUT = 11MHz, in a 20MHz Window, RBW = 30kHz

-

90

-

dBc

SFDR in a Window with EDGE or GSM (Notes 6, 8, 10)

Adjacent Channel Power Ratio,

ACPR with UMTS

fCLK = 76.8MSPS, fOUT = 19.2MHz, RBW = 30kHz (Notes 6, 8, 10) - 70 -

dB

VOLTAGE REFERENCE

Internal Reference Voltage, VFSADJ

Internal Reference Voltage Drift

Pin 18 Voltage with Internal Reference

1.2 1.23

- 40

1.3 V

- ppm/°C

Internal Reference Output Current

Sink/Source Capability

Reference is not intended to be externally loaded

- 0 - µA

Reference Input Impedance

- 1 - M

Reference Input Multiplying Bandwidth (Note 8)

- 1.0 - MHz

DIGITAL INPUTS D11-D0, CLK

Input Logic High Voltage with

3.3V Supply, VIH

Input Logic Low Voltage with

3.3V Supply, VIL

Sleep Input Current, IIH

Input Logic Current, IIH, IL

Clock Input Current, IIH, IL

(Note 5)

(Note 5)

0.7 *

-

-

V

DVDD

- - 0.3 * V

DVDD

-25 - +25 µA

-20 - +20 µA

-10 - +10 µA

5 FN6720.2

December 23, 2013

5 Page

ISL76161

REQ = 0.5 x (RLOAD // RDIFF)

AT EACH OUTPUT

PIN 21

PIN 22

ISL76161

IOUTB

RDIFF

IOUTA

VOUT = (2 x IOUTA x REQ)V

1:1

RLOAD

RLOAD REPRESENTS THE

LOAD SEEN BY THE TRANSFORMER

FIGURE 11. OUTPUT LOADING FOR DATASHEET

MEASUREMENTS

REQ = RA // [ 0.5 x (RLOAD // RDIFF) ], WHERE RA=RB

AT EACH OUTPUT

PIN 21

PIN 22

ISL76161

IOUTB

IOUTA

RA

RDIFF

RB

VOUT = (2 x IOUTA x REQ)V

RLOAD

RLOAD REPRESENTS THE

LOAD SEEN BY THE TRANSFORMER

FIGURE 12. ALTERNATIVE OUTPUT LOADING

Timing Diagram

Propagation Delay

The converter requires two clock rising edges for data to be

represented at the output. Each rising edge of the clock

captures the present data word and outputs the previous

data. The propagation delay is therefore 1/CLK, plus <2ns of

settling. See Figure 13.

CLK

D11-D0

IOUT

tPW1

tPW2

tSU

W0

tHLD

tSU

W1

tPD

tHLD

tSU

W2

tPD

OUTPUT = W0

tHLD

50%

W3

OUTPUT = W-1

OUTPUT = W1

FIGURE 13. PROPAGATION DELAY, SETUP TIME, HOLD TIME AND MINIMUM PULSE WIDTH DIAGRAM

11 FN6720.2

December 23, 2013

11 Page | ||

| Páginas | Total 12 Páginas | |

| PDF Descargar | [ Datasheet ISL76161.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ISL76161 | High Speed D/A Converter | Intersil |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |