|

|

PDF ISL54105 Data sheet ( Hoja de datos )

| Número de pieza | ISL54105 | |

| Descripción | TMDS Regenerator | |

| Fabricantes | Intersil | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ISL54105 (archivo pdf) en la parte inferior de esta página. Total 16 Páginas | ||

|

No Preview Available !

NOT

RECOMSMEEENTDHEE®DISFLO5R41ND05EaAWta

KDeEySFIGeNatSures

Sheet

June 11, 2008

ISL54105

FN6723.0

TMDS Regenerator

The ISL54105 is a high-performance TMDS timing

regenerator containing a programmable equalizer and a

clock data recovery (CDR) function for each of the 3 TMDS

pairs in an HDMI or DVI signal. The TMDS data outputs of

the ISL54105 are regenerated and perfectly aligned to the

regenerated TMDS clock signal, creating an extremely

clean, low-jitter DVI/HDMI signal that can be easily

decoded by any TMDS receiver.

The ISL54105 can be used as a cable extender, to clean up

a noisy/jittery TMDS source, or to provide a very stable

TMDS signal to a finicky DVI or HDMI receiver.

Block Diagram

2

RXC

TERMINATION

Features

• Clock Data Recovery and Retiming

• Programmable pre-emphasis on output driver

• Programmable internal 50Ω, 100Ω, or high-Z termination

• Stand-alone or I2C software-controlled operation

• 72 lead, 10mm x 10mm QFN package

• Pb-free (RoHS compliant)

Applications

• DVI/HDMI extenders

• Televisions/PC monitors/projectors

PLL 2 TXC

2

RX0

2

RX1

2

RX2

CH0

TERMINATION AND

EQUALIZATION

CH1

CH2

RES_TERM

RES_BIAS

BIAS GENERATION

CDR D

CK

D

CDR

CK

D

CDR

CK

FIFO

2 TX0

2

TX1

2

TX2

SDA

SCL

ADDR

7

PD

RESET

CONFIGURATION AND CONTROL

ACTIVITY

DETECT

Ordering Information

PART NUMBER

TEMP. RANGE (°C)

PACKAGE

PKG. DWG. #

ISL54105CRZ

0 to +70

72 Ld QFN (Pb-Free)

L72.10x10B

NOTE: These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100%

matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil

Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

1 CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 1-888-468-3774 | Intersil (and design) is a registered trademark of Intersil Americas Inc.

Copyright Intersil Americas Inc. 2008. All Rights Reserved

All other trademarks mentioned are the property of their respective owners.

1 page

ISL54105

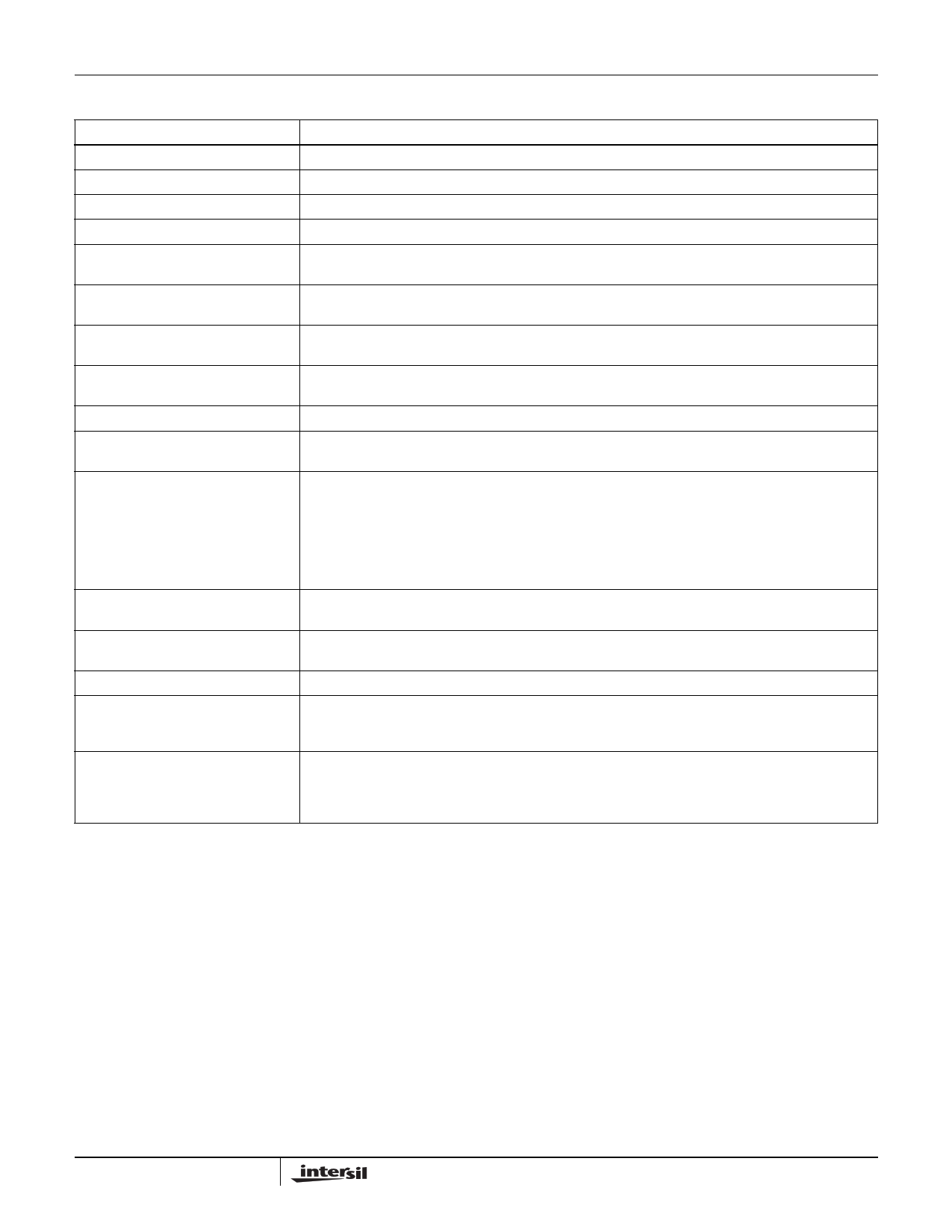

Pin Descriptions

SYMBOL

DESCRIPTION

RX0-, RX0+, RX1-, RX1+, RX2-, RX2+ TMDS Inputs. Incoming TMDS data signals.

RXC-, RXC+

TMDS Inputs. Incoming TMDS clock signals.

TX0-, TX0+, TX1-, TX1+, TX1-, TX1+ TMDS Outputs. TMDS output data for selected channel.

TXC-, TXC+

TMDS Outputs. TMDS output clock for selected channel.

SCL

SDA

ADDR[6:0]

Digital input, 5V tolerant, 500mV hysteresis. Serial data clock for 2-wire interface.

Note: Internal 65kΩ pull-up to VD.

Bidirectional Digital I/O, open drain, 5V tolerant. Serial data I/O for 2-wire interface.

Note: Internal 65kΩ pull-up to VD.

Digital inputs, 5V tolerant. 7-Bit address for serial interface.

Note: Internal 60kΩ pull-down to GND.

AD Digital Output, 3.3V. AD = Activity Detect. Output goes high when an active TMDS clock is detected on

RXC.

RES_BIAS

Tie to GND through a 3.16k external resistor. Sets up internal bias currents.

RES_TERM

Tie to VD through a 1.0k 1% external resistor. During calibration, the termination resistor closest in value

to RES_TERM/20 (= 50Ω) is selected.

PD Digital Input, 3.3V. PD = Power-down. Pull high to put the ISL54105 in a minimum power consumption

mode.

Note: To ensure proper operation, this pin must be held low during power-up. It may be taken high 100ms

after the power supplies have settled to 3.3V ±10%.

When exiting Power-down, a termination resistor Recalibration cycle must be run to re-trim the

termination resistors (see register 0x03[7]).

Note: Internal 60kΩ pull-down to GND.

RESET

Digital Input, 3.3V. Pull high then low to reset the mux. Tie to GND in final application.

Note: Internal 60kΩ pull-down to GND.

TEST

Digital Input. Used for production testing only. Tie to GND in final application. This pin has an internal

pulldown to GND, so it is also acceptable to leave this pin floating.

VD

VD_ESD

THERMAL PAD (GND)

Power supply. Connect to a 3.3V supply and bypass each pin to GND with 0.1µF.

Power supply for ESD protection diodes. Connect one of these pins (pin 41 or 53) to the 3.3V VD supply

rail with a low VF (0.4V or lower) Schottky diode, with the cathode connected to VD_ESD and the anode

connected to VD. Bypass each pin to GND with 0.1µF.

Ground return for the entire chip. The thermal pad must have a low impedance connection to GND for

the ISL54105 to function at all. The lower electrical impedance, the better the ground, and the better the

performance. A low thermal impedance between the thermal pad and the GND plane of the PCB will

dissipate the heat from the package more efficiently as well and is recommended.

5 FN6723.0

June 11, 2008

5 Page

ISL54105

drawing current from the external TMDS receiver it is

attached to.

3.3VTX

VD

3.3VRX

RxN 50

VD_ESD (41, 53)

Tx

TxN

ISL54105

FIGURE 8. ISL54105 ESD PROTECTION DIODES

This is non-ideal and can cause the ISL54105 to fail HDMI

Compliance Test 7-3 (“VOFF”). VOFF is the voltage across

each 50Ω RxN resistor when the power is removed from the

device containing the ISL54105.

Modifying the PCB layout per Figure 9 to add a Schottky

diode between the VD power net and the VD_ESD pins,

eliminates current flow from the ESD bus into VD. This

reduces the amount of current drawn from the Tx supply, but

there is still some circuitry attached to the internal ESD bus

that will sink some current. So the current drawn from Rx will

be lower than if the diode were not there (reducing the VOFF

magnitude), but still not low enough to pass Test 7-3.

3.3VTX

VD

D1

VD_ESD

C1

0.1μF

(41, 53)

Tx

3.3VRX

RxN 50

TxN

ISL54105

FIGURE 9. SCHOTTKY DIODE MODIFICATION

Intersil is currently sampling the ISL54105A, which is fully

compliant with Test 7-3 when applied using the circuit shown

in Figure 9. The ISL54105A is 100% drop-in and backwards

compatible with the ISL54105.

Using the ISL54105A in a layout designed for the ISL54105

(Figure 8) will result in the same behavior as the original

version. See Table 1 for the full matrix.

TABLE 1. VERSION/LAYOUT MATRIX

VERSION

FIGURE 8

FIGURE 9

ISL54105

Fails 7-3

Fails 7-3 (not as badly)

ISL54105A

Fails 7-3

Passes 7-3

Intersil recommends adding the Schottky circuit to all

designs to reduce Rx current drain in systems using the

original version and completely eliminate it in systems using

the ISL54105A.

Inter-Pair (Channel-to-Channel) Skew

The read pointers for Channel 0, 1, and 2 of the FIFO that

follows the CDR all have the same clock, so all 3 channels

transition within a few picoseconds of each other - there is

essentially no skew between the transitions of the three

channels.

However the FIFO read pointers may be positioned up to 2

bits apart relative to each other, introducing a random, fixed

channel-to-channel skew of skew of 1 or (much less

frequently) 2 bits. The random skew is introduced whenever

there is a discontinuity in the input signal (typically a video

mode change or a new mux channel selection). After the

CDRs and PLL lock, the skew is fixed until the next

discontinuity. This adds up to 2 bits of skew in addition to any

incoming skew, as shown in the following examples.

Figure 10 shows an input (the top three signals) with

essentially no skew. After the ISL54105 locks on to the

signal, there may be 1 bit of skew on the output, as shown in

Figure 10.

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Bit 9 Bit 8 B

INPUT SKEW

(none, in this Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Bit 9 Bit 8 B

example)

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Bit 9 Bit 8 B

Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Bit 9 Bit 8 Bit 7 B

OUTPUT SKEW

(1 bit – 615ps at Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Bit 9 Bit 8 B

162.5Mpixels/s)

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Bit 9 Bit 8 B

FIGURE 10. MAXIMUM ADDITIONAL INTERCHANNEL SKEW

FOR INPUTS WITH NO OR LITTLE SKEW

When there is pre-existing skew on the input, the ISL54105

can add up to 2 bits to the channel-to-channel skew. In the

example in Figure 11, the incoming red channel has 2.3 bits

11 FN6723.0

June 11, 2008

11 Page | ||

| Páginas | Total 16 Páginas | |

| PDF Descargar | [ Datasheet ISL54105.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ISL54100 | TMDS Regenerators | Intersil |

| ISL54100A | TMDS Regenerators | Intersil |

| ISL54101 | TMDS Regenerators | Intersil |

| ISL54101A | TMDS Regenerators | Intersil |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |