|

|

PDF ISL6308A Data sheet ( Hoja de datos )

| Número de pieza | ISL6308A | |

| Descripción | Three-Phase Buck PWM Controller | |

| Fabricantes | Intersil | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ISL6308A (archivo pdf) en la parte inferior de esta página. Total 28 Páginas | ||

|

No Preview Available !

ISL6308A

®

Data Sheet

September 9, 2008

FN6669.0

Three-Phase Buck PWM Controller with

High Current Integrated MOSFET Drivers

The ISL6308A is a three-phase PWM control IC with

integrated MOSFET drivers. It provides a precision voltage

regulation system for multiple applications including, but not

limited to, high current low voltage point-of-load converters,

embedded applications and other general purpose low

voltage medium to high current applications.The integration

of power MOSFET drivers into the controller IC marks a

departure from the separate PWM controller and driver

configuration of previous multi-phase product families. By

reducing the number of external parts, this integration allows

for a cost and space saving power management solution.

Output voltage can be programmed using the on-chip DAC

or an external precision reference. A two bit code programs

the DAC reference to one of 4 possible values (0.6V,

0.9V,1.2V and 1.5V). A unity gain, differential amplifier is

provided for remote voltage sensing, compensating for any

potential difference between remote and local grounds. The

output voltage can also be offset through the use of single

external resistor. An optional droop function is also

implemented and can be disabled for applications having

less stringent output voltage variation requirements or

experiencing less severe step loads.

A unique feature of the ISL6308A is the combined use of

both DCR and rDS(ON) current sensing. Load line voltage

positioning and overcurrent protection are accomplished

through continuous inductor DCR current sensing, while

rDS(ON) current sensing is used for accurate channel-current

balance. Using both methods of current sampling utilizes the

best advantages of each technique.

Protection features of this controller IC include a set of

sophisticated overvoltage and overcurrent protection.

Overvoltage results in the converter turning the lower

MOSFETs ON to clamp the rising output voltage and protect

the load. An OVP output is also provided to drive an optional

crowbar device. The overcurrent protection level is set

through a single external resistor. Other protection features

include protection against an open circuit on the remote

sensing inputs. Combined, these features provide advanced

protection for the output load.

Features

• Integrated Multi-Phase Power Conversion

- 1-, 2-, or 3-Phase Operation

• Precision Output Voltage Regulation

- Differential Remote Voltage Sensing

- ±0.8% System Accuracy Over-Temperature

(for REF=0.6V and 0.9V)

- ±0.5% System Accuracy Over-Temperature

(for REF=1.2V and 1.5V)

- Usable for Output Voltages not Exceeding 2.3V

- Adjustable Reference-Voltage Offset

• Precision Channel Current Sharing

- Uses Loss-Less rDS(ON) Current Sampling

• Optional Load Line (Droop) Programming

- Uses Loss-Less Inductor DCR Current Sampling

• Variable Gate-Drive Bias - 5V to 12V

• Internal or External Reference Voltage Setting

- On-Chip Adjustable Fixed DAC Reference Voltage with

2-bit Logic Input Selects from Four Fixed Reference

Voltages (0.6V, 0.9V, 1.2V, 1.5V)

- Reference can be Changed Dynamically

- Can use an External Voltage Reference

• Overcurrent Protection

• Multi-tiered Overvoltage Protection

- OVP Pin to Drive Optional Crowbar Device

• Selectable Operation Frequency up to 1.5MHz per Phase

• Digital Soft-Start

• Capable of Start-up in a Pre-Biased Load

• Pb-Free (RoHS Compliant)

Applications

• High Current DDR/Chipset Core Voltage Regulators

• High Current, Low Voltage DC/DC Converters

• High Current, Low Voltage FPGA/ASIC DC/DC Converters

Ordering Information

PART

NUMBER

PART

MARKING

TEMP. RANGE

(°C)

PACKAGE

PKG.

DWG. #

ISL6308ACRZ* (Note)

ISL6308AIRZ* (Note)

6308A CRZ

6308A IRZ

0 to +70

-40 to +85

40 Ld 6x6 QFN (Pb-free)

40 Ld 6x6 QFN (Pb-free)

L40.6x6

L40.6x6

ISL6308AEVAL1Z

Evaluation Platform

*Add “-T” suffix for tape and reel. Please refer to TB347 for details on reel specifications.

NOTE: These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte

tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free

products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

1 CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 1-888-468-3774 | Intersil (and design) is a registered trademark of Intersil Americas Inc.

Copyright Intersil Americas Inc. 2008. All Rights Reserved

All other trademarks mentioned are the property of their respective owners.

1 page

ISL6308A

Absolute Maximum Ratings

Supply Voltage, VCC . . . . . . . . . . . . . . . . . . . . . . . . . . . -0.3V to +6V

Supply Voltage, PVCC . . . . . . . . . . . . . . . . . . . . . . . . . -0.3V to +15V

Absolute Boot Voltage, VBOOT . . . . . . . . GND - 0.3V to GND + 36V

Phase Voltage, VPHASE . . . . . . . . GND - 0.3V to 15V (PVCC = 12)

GND - 8V (<400ns, 20µJ) to 24V (<200ns, VBOOT-PHASE = 12V)

Upper Gate Voltage, VUGATE . . . . VPHASE - 0.3V to VBOOT + 0.3V

VPHASE - 3.5V (<100ns Pulse Width, 2µJ) to VBOOT + 0.3V

Lower Gate Voltage, VLGATE. . . . . . . . GND - 0.3V to PVCC + 0.3V

GND - 5V (<100ns Pulse Width, 2µJ) to PVCC+ 0.3V

Input, Output, or I/O Voltage . . . . . . . . . GND - 0.3V to VCC + 0.3V

Thermal Information

Thermal Resistance

θJA (°C/W) θJC (°C/W)

QFN Package (Notes 1, 2) . . . . . . . . . .

32

3.5

Maximum Junction Temperature . . . . . . . . . . . . . . . . . . . . . . +150°C

Maximum Storage Temperature Range . . . . . . . . . .-65°C to +150°C

Pb-Free Reflow Profile. . . . . . . . . . . . . . . . . . . . . . . . .see link below

http://www.intersil.com/pbfree/Pb-FreeReflow.asp

Recommended Operating Conditions

VCC Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +5V ±5%

PVCC Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . +5V to 12V ±5%

Ambient Temperature (ISL6308ACRZ) . . . . . . . . . . . . 0°C to +70°C

Ambient Temperature (ISL6308AIRZ) . . . . . . . . . . . .-40°C to +85°C

CAUTION: Stress above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation of the

device at these or any other conditions above those indicated in the operational section of this specification is not implied.

NOTES:

1. θJA is measured in free air with the component mounted on a high effective thermal conductivity test board with “direct attach” features. See

Tech Brief TB379.

2. For θJC, the “case temp” location is the center of the exposed metal pad on the package underside.

Electrical Specifications

Recommended Operating Conditions, Unless Otherwise Specified. Parameters with MIN and/or MAX limits are

100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are

not production tested.

PARAMETER

TEST CONDITIONS

MIN TYP MAX UNITS

BIAS SUPPLY AND INTERNAL OSCILLATOR

Input Bias Supply Current

Gate Drive Bias Current

VCC POR (Power-On Reset) Threshold

IVCC; ENLL = high

IPVCC; ENLL = high; all gate outputs open,

Fsw = 250kHz

VCC Rising

12

0.4

4.25

15

0.8

4.38

18 mA

1.2 mA

4.47 V

VCC Falling

3.75 3.88 4.00 V

PVCC POR (Power-On Reset) Threshold

PVCC Rising

4.25 4.38 4.47 V

PVCC Falling

3.75 3.88 4.00 V

Oscillator Frequency

Fsw

225 250 275 kHz

Oscillator Ramp Amplitude (Note 3)

Maximum Duty Cycle (Note 3)

VP-P

- 1.50 - V

- 66.6 - %

CONTROL THRESHOLDS

ENLL Rising Threshold

0.595 0.630 0.670 V

ENLL Hysteresis

28 35 43 mV

ENLL Pull-Up current

ENLL = 1V

-0.5 -1.4 -3.0 µA

COMP Shutdown Threshold

COMP Falling

0.1 0.25 0.4 V

REFERENCE AND DAC

System Accuracy (DAC = 0.6V, 0.9V)

DROOP connected to IREF

-0.8 -

0.8 %

System Accuracy (DAC = 1.2V, 1.50V)

DROOP connected to IREF

-0.5 -

0.5 %

DAC Input Low Voltage (REF0, REF1)

- - 0.4 V

DAC Input High Voltage (REF0, REF1)

0.8 -

-V

Minimum External Reference (Note 4)

REF pin input

- 0.6 - V

5 FN6669.0

September 9, 2008

5 Page

ISL6308A

MOSFET driver detects the change in state of the PWM

signal and turns off the synchronous MOSFET and turns on

the upper MOSFET. The PWM signal will remain high until

the pulse termination signal marks the beginning of the next

cycle by triggering the PWM signal low.

Channel Current Balance

One important benefit of multi-phase operation is the thermal

advantage gained by distributing the dissipated heat over

multiple devices and greater area. By doing this the designer

avoids the complexity of driving parallel MOSFETs and the

expense of using expensive heat sinks and exotic magnetic

materials.

In order to realize the thermal advantage, it is important that

each channel in a multi-phase converter be controlled to

carry about the same amount of current at any load level. To

achieve this, the currents through each channel must be

sampled every switching cycle. The sampled currents, In,

from each active channel are summed together and divided

by the number of active channels. The resulting cycle

average current, IAVG, provides a measure of the total load

current demand on the converter during each switching

cycle. Channel current balance is achieved by comparing

the sampled current of each channel to the cycle average

current, and making the proper adjustment to each channel

pulse width based on the error. Intersil’s patented current-

balance method is illustrated in Figure 3, with error

correction for channel 1 represented. In the figure, the cycle

average current, IAVG, is compared with the Channel 1

sample, I1, to create an error signal IER.

The filtered error signal modifies the pulse width

commanded by VCOMP to correct any unbalance and force

IER toward zero. The same method for error signal

correction is applied to each active channel.

VCOMP

+

-

FILTER f(s)

+ PWM1

-

SAWTOOTH SIGNAL

IER

IAVG

- ÷N

+

Σ

TO GATE

CONTROL

LOGIC

I3

I2

I1

NOTE: Channel 2 and 3 are optional.

FIGURE 3. CHANNEL 1 PWM FUNCTION AND CURRENT-

BALANCE ADJUSTMENT

Current Sampling

In order to realize proper current balance, the currents in

each channel must be sampled every switching cycle. This

sampling occurs during the forced off-time, following a PWM

transition low. During this time the current sense amplifier

uses the ISEN inputs to reproduce a signal proportional to

the inductor current, IL. This sensed current, ISEN, is simply

a scaled version of the inductor current. The sample window

opens exactly 1/6 of the switching period, tSW, after the

PWM transitions low. The sample window then stays open

the rest of the switching cycle until PWM transitions high

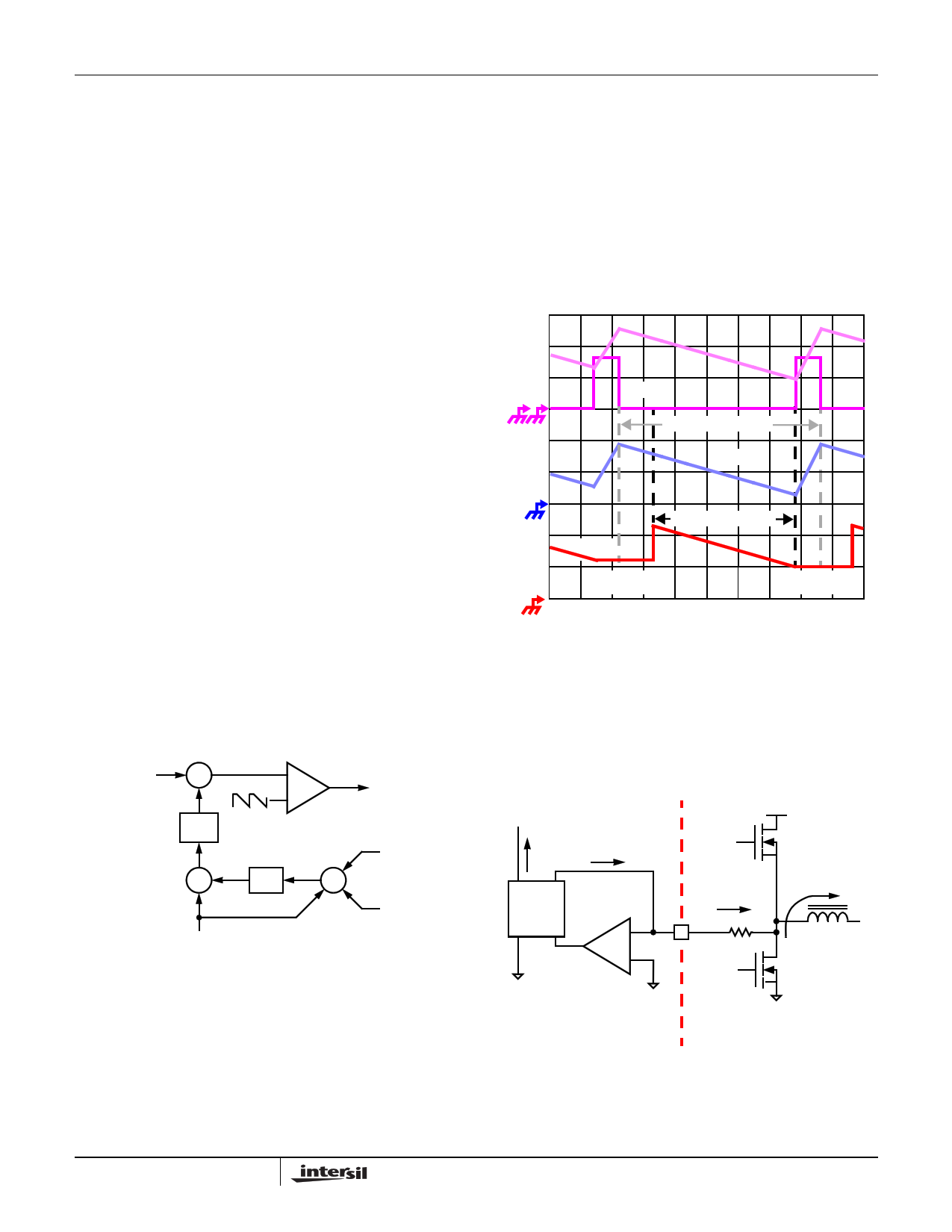

again, as illustrated in Figure 4.

The sampled current, at the end of the tSAMPLE, is

proportional to the inductor current and is held until the next

switching period sample. The sampled current is used only

for channel current balance.

IL

PWM

SWITCHING PERIOD

ISEN

SAMPLING PERIOD

OLD SAMPLE

CURRENT

NEW SAMPLE

CURRENT

TIME

FIGURE 4. SAMPLE AND HOLD TIMING

The ISL6308A supports MOSFET rDS(ON) current sensing

to sample each channel’s current for channel current

balance. The internal circuitry, shown in Figure 5 represents

Channel N of an N-channel converter. This circuitry is

repeated for each channel in the converter, but may not be

active depending on the status of the PVCC3 and PVCC2

pins, as described in “PWM Operation” on page 10.

In

ISEN

=

IL

x -r--D-----S----(---O-----N-----)

RISEN

VIN

CHANNEL N

UPPER MOSFET

SAMPLE

AND

HOLD

-

+

ISL6308A INTERNAL CIRCUIT

IL

ISEN(n)

RISEN

-

ILx rDS(ON)

+

CHANNEL N

LOWER MOSFET

EXTERNAL CIRCUIT

FIGURE 5. ISL6308A INTERNAL AND EXTERNAL CURRENT-

SENSING CIRCUITRY FOR CURRENT BALANCE

11 FN6669.0

September 9, 2008

11 Page | ||

| Páginas | Total 28 Páginas | |

| PDF Descargar | [ Datasheet ISL6308A.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ISL6308 | Three-Phase Buck PWM Controller with High Current Integrated MOSFET Drivers | Intersil Corporation |

| ISL6308A | Three-Phase Buck PWM Controller | Intersil |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |