|

|

PDF CY7C63833 Data sheet ( Hoja de datos )

| Número de pieza | CY7C63833 | |

| Descripción | Low-Speed USB Peripheral Controller | |

| Fabricantes | Cypress Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de CY7C63833 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

CY7C63310

CY7C638xx

enCoRe™ II

Low-Speed USB Peripheral Controller

1.0 Features

• enCoReTM II USB—“enhanced Component Reduction”

— Crystalless oscillator with support for an external clock.

The internal oscillator eliminates the need for an external

crystal or resonator

— Two internal 3.3V regulators and internal USB pull-up

resistor

www.DataSheet4U.com

— Configurable IO for real-world interface without external

components

• USB Specification Compliance

— Conforms to USB Specification, Version 2.0

— Conforms to USB HID Specification, Version 1.1

— Supports one Low-Speed USB device address

— Supports one control endpoint and two data endpoints

— Integrated USB transceiver with dedicated 3.3V

regulator for USB signalling and D- pull up.

• Enhanced 8-bit microcontroller

— Harvard architecture

— M8C CPU speed can be up to 24 MHz or sourced by an

external clock signal

• Internal memory

— Up to 256 bytes of RAM

— Up to eight Kbytes of Flash including EEROM emulation

• Interface can autoconfigure to operate as PS/2 or USB

— No external components for switching between PS/2 and

USB modes

— No GPIO pins needed to manage dual-mode capability

• Low power consumption

— Typically 10 mA at 6 MHz

— 10 µA sleep

• In-system re-programmability

— Allows easy firmware update

• General purpose I/O ports

— Up to 20 General Purpose I/O (GPIO) pins

— High current drive on GPIO pins. Configurable 8- or 50-

mA/pin current sink on designated pins

— Each GPIO port supports high-impedance inputs,

configurable pull up, open drain output, CMOS/TTL

inputs, and CMOS output

— Maskable interrupts on all I/O pins

• A dedicated 3.3V regulator for the USB PHY. Aids in

signalling and D-line pull-up

• 125 mA 3.3V voltage regulator can power external 3.3V

devices

• 3.3V I/O pins

— 4 I/O pins with 3.3V logic levels

— Each 3.3V pin supports high-impedance input, internal

pull up, open drain output or traditional CMOS output

• SPI serial communication

— Master or slave operation

— Configurable up to 4 Mbit/second transfers in the master

mode

— Supports half duplex single data line mode for optical

sensors

• 2-channel 8-bit or 1-channel 16-bit capture timer registers.

Capture timer registers store both rising and falling edge

times

— Two registers each for two input pins

— Separate registers for rising and falling edge capture

— Simplifies interface to RF inputs for wireless applications

• Internal low-power wake-up timer during suspend mode

— Periodic wake-up with no external components

• 12-bit Programmable Interval Timer with interrupts

• Advanced development tools based on Cypress

MicroSystems PSoC™ tools

• Watchdog timer (WDT)

• Low-voltage detection with user-configurable threshold

voltages

• Operating voltage from 4.0V to 5.5VDC

• Operating temperature from 0–70°C

• Available in 16/18-pin PDIP, 16/18/24-pin SOIC, 24-pin

QSOP and 32-lead QFN packages

• Industry standard programmer support

1.1 Applications

The CY7C63310/CY7C638xx is targeted for the following

applications:

• PC HID devices

— Mice (optomechanical, optical, trackball)

• Gaming

— Joysticks

— Game pad

• General-purpose

— Barcode scanners

— POS terminal

— Consumer electronics

— Toys

— Remote controls

— Security dongles

Cypress Semiconductor Corporation • 198 Champion Court • San Jose, CA 95134-1709 • 408-943-2600

Document 38-08035 Rev. *I

Revised September 26, 2006

[+] Feedback

1 page

CY7C63310

CY7C638xx

5.1 Pinouts Assignments

Table 5-1. Pin Assignments

32 24 24 18

QFN QSOP SOIC SIOC

18

PDIP

16

SOIC

16

PDIP

Name

Description

21 19 18

22 20 19

P3.0

P3.1

GPIO Port 3 – configured as a group (byte)

9 11 11

8 10 10

P2.0

P2.1

GPIO Port 2 – configured as a group (byte)

www.DataSheet4U1.c4om 14 13 10 15 9 13 P1.0/D+ GPIO Port 1 bit 0/USB D+[1] If this pin is used as a

General Purpose output, it will draw current. This pin

must be configured as an input to reduce current

draw.

15 15 14 11 16 10 14 P1.1/D– GPIO Port 1 bit 1/USB D–[1] If this pin is used as a

General Purpose output, it will draw current. This pin

must be configured as an input to reduce current

draw.

18 17 16 13 18 12 16 P1.2/VREG GPIO Port 1 bit 2—Configured individually.

3.3V if regulator is enabled. (The 3.3V regulator is not

available in the CY7C63310 and CY7C63801.) A 1-µF

min, 2-µF max capacitor is required on Vreg output.

20 18 17 14 1 13 1 P1.3/SSEL GPIO Port 1 bit 3—Configured individually.

Alternate function is SSEL signal of the SPI bus TTL

voltage thresholds. Although Vreg is not available

with the CY7C63310, 3.3V I/O is still available.

23 21 20 15 2 14 2 P1.4/SCLK GPIO Port 1 bit 4—Configured individually.

Alternate function is SCLK signal of the SPI bus TTL

voltage thresholds. Although Vreg is not available

with the CY7C63310, 3.3V I/O is still available.

24 22 21 16 3 15 3 P1.5/SMOSI GPIO Port 1 bit 5—Configured individually.

Alternate function is SMOSI signal of the SPI bus TTL

voltage thresholds. Although Vreg is not available

with the CY7C63310, 3.3V I/O is still available.

25 23 22 17 4 16 4 P1.6/SMISO GPIO Port 1 bit 6—Configured individually.

Alternate function is SMISO signal of the SPI bus TTL

voltage thresholds. Although Vreg is not available

with the CY7C63310, 3.3V I/O is still available.

26 24 23 18

5

P1.7

GPIO Port 1 bit 7—Configured individually.

TTL voltage threshold.

7 9 9 8 13 7 11 P0.0 GPIO Port 0 bit 0—Configured individually.

On CY7C638xx and CY7C63310, external clock

input when configured as Clock In.

6 8 8 7 12 6 10 P0.1 GPIO Port 0 bit 1—Configured individually

On CY7C638xx and CY7C63310, clock output when

configured as Clock Out.

5 7 7 6 11 5 9 P0.2/INT0 GPIO port 0 bit 2—Configured individually

Optional rising edge interrupt INT0

4 6 6 5 10 4 8 P0.3/INT1 GPIO port 0 bit 3—Configured individually

Optional rising edge interrupt INT1

3 5 5 4 9 3 7 P0.4/INT2 GPIO port 0 bit 4—Configured individually

Optional rising edge interrupt INT2

Note

1. P1.0(D+) and P1.1(D-) pins must be in I/O mode when used as GPIO and in Isb mode.

Document 38-08035 Rev. *I

Page 5 of 74

[+] Feedback

5 Page

CY7C63310

CY7C638xx

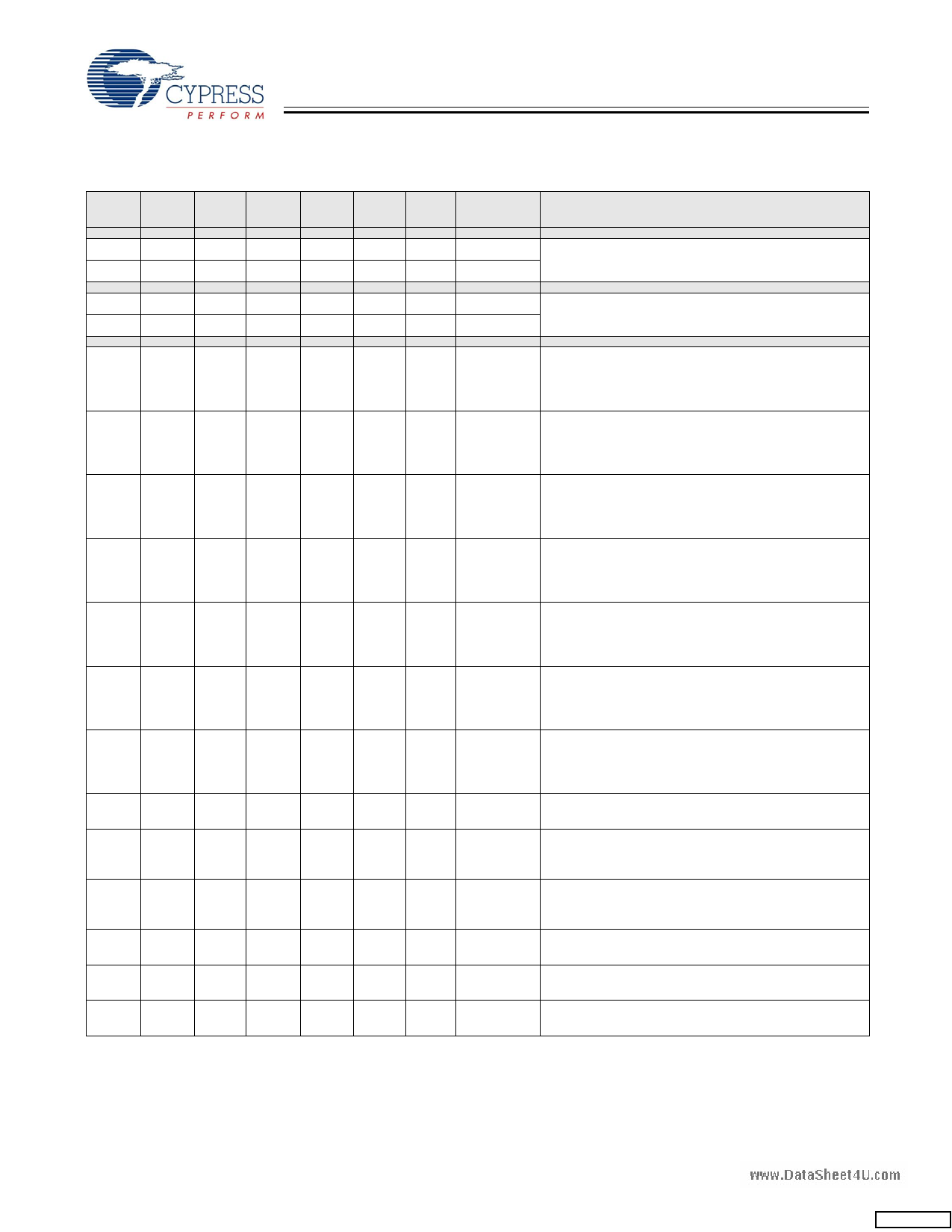

8.0 Instruction Set Summary

Instruction Set Summary tables are described in detail in the

PSoC Designer Assembly Language User Guide (available on

The instruction set is summarized in Table 8-1 numerically and the www.cypress.com web site).

serves as a quick reference. If more information is needed, the

Table 8-1. Instruction Set Summary Sorted Numerically by Opcode Order[2, 3]

00 15

01 4

02 6

03 7

www.DataSheet40U4.co7m

05 8

06 9

07 10

08 4

09 4

0A 6

0B 7

0C 7

0D 8

0E 9

0F 10

10 4

11 4

12 6

13 7

14 7

15 8

16 9

17 10

18 5

19 4

1A 6

1B 7

1C 7

1D 8

1E 9

1F 10

20 5

21 4

22 6

23 7

24 7

25 8

26 9

27 10

28 11

29 4

2A 6

2B 7

2C 7

Instruction Format

1 SSC

2 ADD A, expr

2 ADD A, [expr]

2 ADD A, [X+expr]

2 ADD [expr], A

2 ADD [X+expr], A

3 ADD [expr], expr

3 ADD [X+expr], expr

1 PUSH A

2 ADC A, expr

2 ADC A, [expr]

2 ADC A, [X+expr]

2 ADC [expr], A

2 ADC [X+expr], A

3 ADC [expr], expr

3 ADC [X+expr], expr

1 PUSH X

2 SUB A, expr

2 SUB A, [expr]

2 SUB A, [X+expr]

2 SUB [expr], A

2 SUB [X+expr], A

3 SUB [expr], expr

3 SUB [X+expr], expr

1 POP A

2 SBB A, expr

2 SBB A, [expr]

2 SBB A, [X+expr]

2 SBB [expr], A

2 SBB [X+expr], A

3 SBB [expr], expr

3 SBB [X+expr], expr

1 POP X

2 AND A, expr

2 AND A, [expr]

2 AND A, [X+expr]

2 AND [expr], A

2 AND [X+expr], A

3 AND [expr], expr

3 AND [X+expr], expr

1 ROMX

2 OR A, expr

2 OR A, [expr]

2 OR A, [X+expr]

2 OR [expr], A

Flags

C, Z

C, Z

C, Z

C, Z

C, Z

C, Z

C, Z

C, Z

C, Z

C, Z

C, Z

C, Z

C, Z

C, Z

C, Z

C, Z

C, Z

C, Z

C, Z

C, Z

C, Z

Z

C, Z

C, Z

C, Z

C, Z

C, Z

C, Z

C, Z

Z

Z

Z

Z

Z

Z

Z

Z

Z

Z

Z

Z

2D 8

2E 9

2F 10

30 9

31 4

32 6

33 7

34 7

35 8

36 9

37 10

38 5

39 5

3A 7

3B 8

3C 8

3D 9

3E 10

3F 10

40 4

41 9

42 10

43 9

44 10

45 9

46 10

47 8

48 9

49 9

4A 10

4B 5

4C 7

4D 7

4E 5

4F 4

50 4

51 5

52 6

53 5

54 6

55 8

56 9

57 4

58 6

59 7

Instruction Format

2 OR [X+expr], A

3 OR [expr], expr

3 OR [X+expr], expr

1 HALT

2 XOR A, expr

2 XOR A, [expr]

2 XOR A, [X+expr]

2 XOR [expr], A

2 XOR [X+expr], A

3 XOR [expr], expr

3 XOR [X+expr], expr

2 ADD SP, expr

2 CMP A, expr

2 CMP A, [expr]

2 CMP A, [X+expr]

3 CMP [expr], expr

3 CMP [X+expr], expr

2 MVI A, [ [expr]++]

2 MVI [ [expr]++], A

1 NOP

3 AND reg[expr], expr

3 AND reg[X+expr], expr

3 OR reg[expr], expr

3 OR reg[X+expr], expr

3 XOR reg[expr], expr

3 XOR reg[X+expr], expr

3 TST [expr], expr

3 TST [X+expr], expr

3 TST reg[expr], expr

3 TST reg[X+expr], expr

1 SWAP A, X

2 SWAP A, [expr]

2 SWAP X, [expr]

1 SWAP A, SP

1 MOV X, SP

2 MOV A, expr

2 MOV A, [expr]

2 MOV A, [X+expr]

2 MOV [expr], A

2 MOV [X+expr], A

3 MOV [expr], expr

3 MOV [X+expr], expr

2 MOV X, expr

2 MOV X, [expr]

2 MOV X, [X+expr]

Flags

Z 5A 5

Z 5B 4

Z 5C 4

5D 6

Z 5E 7

Z 5F 10

Z 60 5

Z 61 6

Z 62 8

Z 63 9

Z 64 4

65 7

66 8

if (A=B) Z=1

if (A<B) C=1

67

68

69

4

7

8

6A 4

Z 6B 7

6C 8

6D 4

Z 6E 7

Z 6F 8

Z 70 4

Z 71 4

Z 72 4

Z 73 4

Z 74 4

Z 75 4

Z 76 7

Z 77 8

Z 78 4

Z 79 4

7A 7

Z 7B 8

7C 13

Z 7D 7

Z 7E 10

Z 7F 8

8x 5

9x 11

Ax 5

Bx 5

Cx 5

Dx 5

Ex 7

Fx 13

Instruction Format

2 MOV [expr], X

1 MOV A, X

1 MOV X, A

2 MOV A, reg[expr]

2 MOV A, reg[X+expr]

3 MOV [expr], [expr]

2 MOV reg[expr], A

2 MOV reg[X+expr], A

3 MOV reg[expr], expr

3 MOV reg[X+expr], expr

1 ASL A

2 ASL [expr]

2 ASL [X+expr]

1 ASR A

2 ASR [expr]

2 ASR [X+expr]

1 RLC A

2 RLC [expr]

2 RLC [X+expr]

1 RRC A

2 RRC [expr]

2 RRC [X+expr]

2 AND F, expr

2 OR F, expr

2 XOR F, expr

1 CPL A

1 INC A

1 INC X

2 INC [expr]

2 INC [X+expr]

1 DEC A

1 DEC X

2 DEC [expr]

2 DEC [X+expr]

3 LCALL

3 LJMP

1 RETI

1 RET

2 JMP

2 CALL

2 JZ

2 JNZ

2 JC

2 JNC

2 JACC

2 INDEX

Flags

Z

Z

Z

C, Z

C, Z

C, Z

C, Z

C, Z

C, Z

C, Z

C, Z

C, Z

C, Z

C, Z

C, Z

C, Z

C, Z

C, Z

Z

C, Z

C, Z

C, Z

C, Z

C, Z

C, Z

C, Z

C, Z

C, Z

Z

Notes

2. Interrupt routines take 13 cycles before execution resumes at interrupt vector table.

3. The number of cycles required by an instruction is increased by one for instructions that span 256-byte boundaries in the Flash memory space.

Document 38-08035 Rev. *I

Page 11 of 74

[+] Feedback

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet CY7C63833.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| CY7C63833 | Low-Speed USB Peripheral Controller | Cypress Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |