|

|

PDF IDT70V9389 Data sheet ( Hoja de datos )

| Número de pieza | IDT70V9389 | |

| Descripción | HIGH-SPEED 3.3V 64K x18/x16 SYNCHRONOUS PIPELINED DUAL-PORT STATIC RAM | |

| Fabricantes | IDT | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de IDT70V9389 (archivo pdf) en la parte inferior de esta página. Total 19 Páginas | ||

|

No Preview Available !

HIGH-SPEED 3.3V

64K x18/x16

SYNCHRONOUS PIPELINED IDT70V9389/289L

DUAL-PORT STATIC RAM

Features:

◆ True Dual-Ported memory cells which allow simultaneous

access of the same memory location

◆ High-speed clock to data access

– Commercial: 7.5/9/12ns (max.)

– Industrial: 9ns (max.)

◆ Low-power operation

– IDT70V9389/289L

Active: 500mW (typ.)

Standby: 1.5mW (typ.)

◆ Flow-Through or Pipelined output mode on either port via

the FT/PIPE pins

◆ Counter enable and reset features

◆ Dual chip enables allow for depth expansion without

additional logic

◆ LVTTL- compatible, single 3.3V (±0.3V) power supply

Functional Block Diagram

◆ Full synchronous operation on both ports

– 4ns setup to clock and 0ns hold on all control, data, and

address inputs

– Data input, address, and control registers

– Fast 7.5ns clock to data out in the Pipelined output mode

– Self-timed write allows fast cycle time

– 12ns cycle time, 83MHz operation in Pipelined output

mode

◆ Separate upper-byte and lower-byte controls for

multiplexed bus and bus matching compatibility

◆ Industrial temperature range (–40°C to +85°C) is

available for selected speeds

◆ Available in a 128-pin Thin Quad Flatpack (TQFP) and

100-pin Thin Quad Flatpack (TQFP)

◆ Green parts available, see ordering information

R/WL

UBL

CE0L

CE1L

LBL

OEL

1

0

0/1

R/WR

UBR

CE0R

1

0

CE1R

0/1

LBR

OER

FT/PIPEL

I/O9L-I/O17L(2)

I/O0L-I/O8L(1)

A15L

A0L

CLKL

ADSL

CNTENL

CNTRSTL

0/1 1b 0b b a 1a 0a

Counter/

Address

Reg.

I/O

Control

I/O

Control

MEMORY

ARRAY

0a 1a

a

b0b 1b

0/1

Counter/

Address

Reg.

FT/PIPER

I/O9R-I/O17R(1)

I/O0R-I/O8R(1)

A15R

A0R

CLKR

ADSR

CNTENR

CNTRSTR

4856 drw 01

NOTES:

1. I/O0X - I/O7X for IDT70V9289.

2. I/O8X - I/O15X for IDT70V9289.

©2014 Integrated Device Technology, Inc.

1

MARCH 2014

DSC-4856/8

1 page

IDT70V9389/289L

High-Speed 3.3V 64K x18/x16 Dual-Port Synchronous Pipelined Static RAM

Pin Configurations(1,2,3)(con't.)

Industrial & Commercial Temperature Ranges

02/25/14

Index

A9L

A10L

A11L

A12L

A13L

A14L

A15L

NC

NC

LBL

UBL

CE0L

CE1L

CNTRSTL

VDD

R/WL

OEL

FT/PIPEL

VSS

I/O15L

I/O14L

I/O13L

I/O12L

I/O11L

I/O10L

1100

99 98

97

96

95

94

93

92

91

90

89

88

87 86

85 84

83

82

81

80

79

78

77

76

75

2 74

3 73

4 72

5 71

6 70

7 69

8 68

9 67

10 IDT70V9289PF

11 PN100(4)

12

66

65

64

13 100-Pin TQFP

14 Top View(5)

15

63

62

61

16 60

17 59

18 58

19 57

20 56

21 55

22 54

23 53

24 52

25 51

26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50

A9R

A10R

A11R

A12R

A13R

A14R

A15R

NC

NC

LBR

UBR

CE0R

CE1R

.

CNTRSTR

VSS

R/WR

OER

FT/PIPER

VSS

I/O15R

I/O14R

I/O13R

I/O12R

I/O11R

I/O10R

4856 drw 02c

NOTES:

1. All VDD pins must be connected to power supply.

2. All VSS pins must be connected to ground.

3. Package body is approximately 14mm x 14mm x 1.4mm

4. This package code is used to reference the package diagram.

5. This text does not indicate orientation of the actual part-marking.

6.452

5 Page

IDT70V9389/289L

High-Speed 3.3V 64K x18/x16 Dual-Port Synchronous Pipelined Static RAM

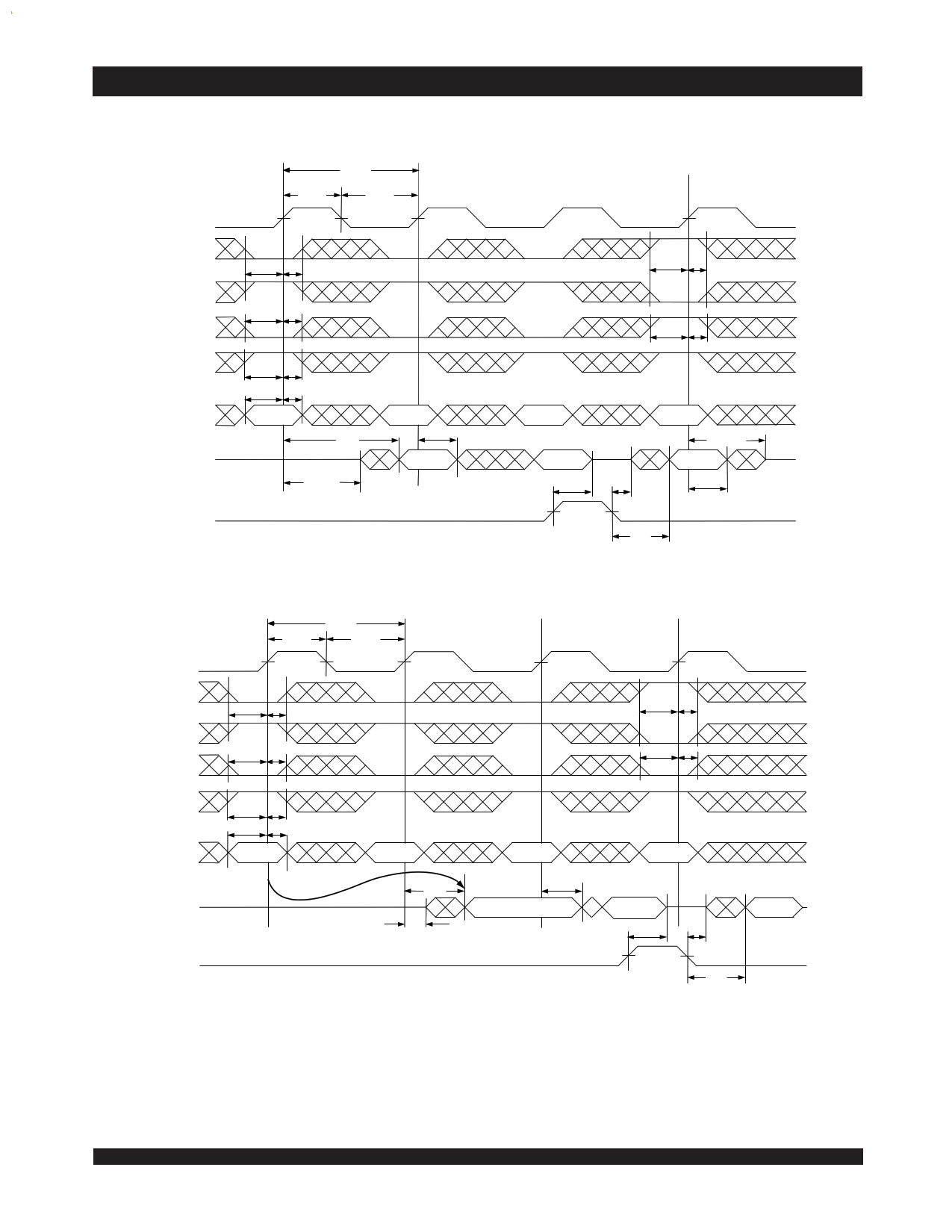

Timing Waveform of Read Cycle for

Flow-Through Output (FT/PIPE"X" = VIL)(3,7)

tCH1

tCYC1

tCL1

CLK

CE0

tSC tHC

CE1

UB, LB

tSB tHB

Industrial & Commercial Temperature Ranges

tSC tHC

tSB tHB

R/W

ADDRESS(5)

DATAOUT

OE (2)

tSW tHW

tSA tHA

An

tCD1

tCKLZ(1)

An + 1

tDC

Qn

An + 2

Qn + 1

(1)

tOHZ

An + 3

tCKHZ (1)

Qn + 2

tOLZ (1)

tDC

tOE

..

4856 drw 06

Timing Waveform of Read Cycle for Pipelined Operation

(FT/PIPE"X" = VIH)(3,7)

tCH2

tCYC2

tCL2

CLK

CE0

CE1

UB, LB

tSC tHC

tSB tHB

tSC tHC

(4)

tSB tHB

(6)

R/W

ADDRESS(5)

tSW tHW

tSA tHA

An

An + 1

An + 2

An + 3

DATAOUT

(1 Latency)

tCKLZ(1)

tCD2

tDC

Qn

Qn + 1

tOHZ(1)

Qn + 2(6)

tOLZ(1)

OE (2)

tOE

NOTES:

4856 drw 07

1. Transition is measured 0mV from Low or High-impedance voltage with the Output Test Load (Figure 2).

2. OE is asynchronously controlled; all other inputs are synchronous to the rising clock edge.

3. ADS = VIL and CNTRST = VIH.

4. The output is disabled (High-Impedance state) by CE0 = VIH, CE1 = VIL, UB = VIH, or LB = VIH following the next rising edge of the clock. Refer to Truth Table 1.

5. Addresses do not have to be accessed sequentially since ADS = VIL constantly loads the address on the rising edge of the CLK; numbers

are for reference use only.

6. If UB or LB was HIGH, then the Upper Byte and/or Lower Byte of DATAOUT for Qn + 2 would be disabled (High-Impedance state).

7. "X' here denotes Left or Right port. The diagram is with respect to that port.

6.1412

11 Page | ||

| Páginas | Total 19 Páginas | |

| PDF Descargar | [ Datasheet IDT70V9389.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| IDT70V9389 | HIGH-SPEED 3.3V 64K x18/x16 SYNCHRONOUS PIPELINED DUAL-PORT STATIC RAM | IDT |

| IDT70V9389L | HIGH-SPEED 3.3V 64K x18/x16 SYNCHRONOUS PIPELINED DUAL-PORT STATIC RAM | IDT |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |