|

|

PDF AD7151 Data sheet ( Hoja de datos )

| Número de pieza | AD7151 | |

| Descripción | Capacitance Converter | |

| Fabricantes | Analog Devices | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AD7151 (archivo pdf) en la parte inferior de esta página. Total 29 Páginas | ||

|

No Preview Available !

Ultra-Low Power, 1-Channel, Capacitance

Converter for Proximity Sensing

AD7151

FEATURES

Ultra-low power

2.7 V to 3.6 V, 70 μA

Response time: 10 ms

Adaptive environmental compensation

1 capacitance input channel

Sensor capacitance (CSENS) 0 pF up to 13 pF

Sensitivity to 1 fF

EMC tested

2 modes of operation

Standalone with fixed settings

Interfaced to a microcontroller for user-defined settings

Proximity detection output flag

2-wire serial interface (I2C compatible)

Operating temperature

−40°C to +85°C

10-lead MSOP package

APPLICATIONS

Proximity sensing

Contactless switching

Position detection

Level detection

GENERAL DESCRIPTION

The AD7151 delivers a complete signal processing solution for

capacitive proximity sensors, featuring an ultra-low power

converter with fast response time. The AD7150 is a 2-channel

alternative to the AD7151.

The AD7151 uses Analog Devices, Inc., capacitance-to-digital

converter (CDC) technology, which combines features

important for interfacing to real sensors, such as high input

sensitivity and high tolerance of both input parasitic ground

capacitance and leakage current.

The integrated adaptive threshold algorithm compensates for

any variations in the sensor capacitance due to environmental

factors like humidity and temperature or due to changes in the

dielectric material over time.

By default, the AD7151 operates in standalone mode using the

fixed power-up settings and indicates detection on a digital

output. Alternatively, the AD7151 can be interfaced to a

microcontroller via the serial interface, the internal registers can

be programmed with user-defined settings, and the data and

status can be read from the part.

The AD7151 operates with a 2.7 V to 3.6 V power supply. It is

specified over the temperature range of −40°C to +85°C.

CSENS

FUNCTIONAL BLOCK DIAGRAM

VDD

CIN

Σ-Δ CDC

DIGITAL

FILTER

AD7151

SERIAL

INTERFACE

EXC

EXCITATION

THRESHOLD

SCL

SDA

OUT

GND

Figure 1.

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarksandregisteredtrademarksarethepropertyoftheirrespectiveowners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.461.3113

©2007 Analog Devices, Inc. All rights reserved.

1 page

AD7151

Parameter

Min Typ Max Unit1

POWER REQUIREMENTS

VDD-to-GND Voltage

2.7

3.6 V

IDD Current4

IDD Current Power-Down Mode4

70 80 μA

1 5 μA

3 10 μA

Test Conditions/Comments

VDD = 3.3 V, nominal

Temperature ≤ 25°C

Temperature = 85°C

1 Capacitance units: one picofarad (1 pF) = 1 × 10−12 farad (F); one femtofarad (1 fF) = 10−15 farad (F).

2 The CAPDAC can be used to shift (offset) the input range. The total capacitance of the sensor can, therefore, be up to the sum of the CAPDAC value and the conversion

input range. With the autoCAPDAC feature, the CAPDAC is adjusted automatically when the CDC input value is lower than 25% or higher than 75% of the CDC

nominal input range.

3 Specification is not production tested but is supported by characterization data at initial product release.

4 Digital inputs equal to VDD or GND.

TIMING SPECIFICATIONS

VDD = 2.7 V to 3.6 V; GND = 0 V; Input Logic 0 = 0 V; Input Logic 1 = VDD; –40°C to +85°C, unless otherwise noted.

Table 2.

Parameter

CONVERTER

Conversion Time

Wake-Up Time from Power-Down Mode1, 2

Power-Up Time1, 3

Reset Time1, 4

SERIAL INTERFACE5, 6

SCL Frequency

SCL High Pulse Width, tHIGH

SCL Low Pulse Width, tLOW

SCL, SDA Rise Time, tR

SCL, SDA Fall Time, tF

Hold Time (Start Condition), tHD;STA

Setup Time (Start Condition), tSU;STA

Data Setup Time, tSU;DAT

Setup Time (Stop Condition), tSU;STO

Data Hold Time (Master), tHD;DAT

Bus-Free Time (Between Stop and Start Condition), tBUF

Min Typ Max

10

0.3

2

2

0 400

0.6

1.3

0.3

0.3

0.6

0.6

0.1

0.6

10

1.3

Unit

ms

ms

ms

ms

kHz

μs

μs

μs

μs

μs

μs

μs

μs

ns

μs

Test Conditions/Comments

See Figure 2.

After this period, the first clock is generated.

Relevant for repeated start condition.

1 Specification is not production tested but is supported by characterization data at initial product release.

2 Wake-up time is the maximum delay between the last SCL edge writing the configuration register and the start of conversion.

3 Power-up time is the maximum delay between the VDD crossing the minimum level (2.7 V) and either the start of conversion or when ready to receive a serial interface

command.

4 Reset time is the maximum delay between the last SCL edge writing the reset command and either the start of conversion or when ready to receive a serial interface

command.

5 Sample tested during initial release to ensure compliance.

6 All input signals are specified with input rise/fall times = 3 ns, measured between the 10% and 90% points. Timing reference points at 50% for inputs and outputs.

Output load = 10 pF.

tLOW tR

tF

tHD;STA

SCL

tHD;STA

tHD;DAT

tHIGH

tSU;DAT

tSU;STA

tSU;STO

SDA

tBUF

PS

S

Figure 2. Serial Interface Timing Diagram

P

Rev. 0 | Page 4 of 28

5 Page

AD7151

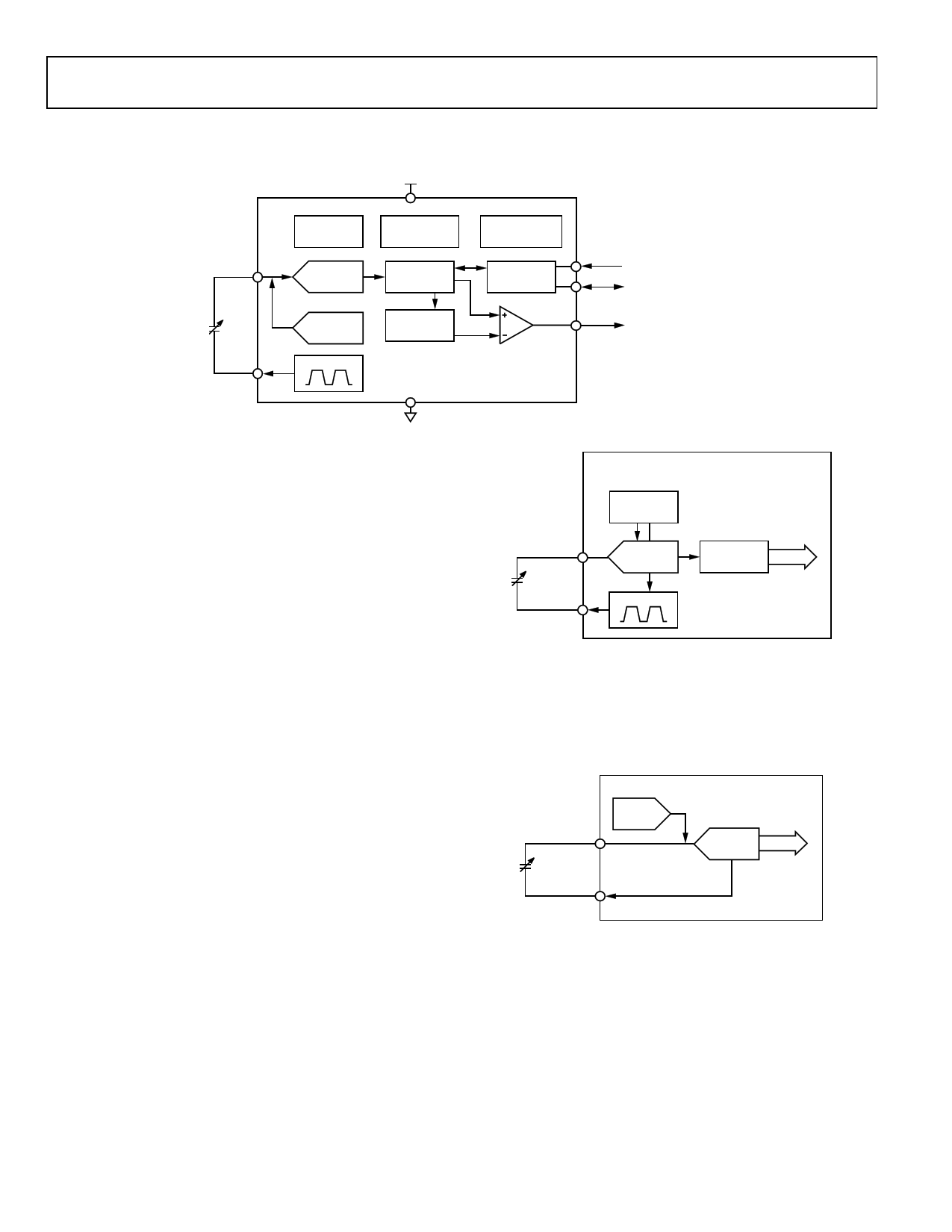

ARCHITECTURE AND MAIN FEATURES

3.3V

VDD

CLOCK

GENERATOR

POWER-DOWN

TIMER

POWER SUPPLY

MONITOR

SCL

CIN

Σ-Δ CDC

DIGITAL

FILTER

SERIAL

INTERFACE

PROGRAMMING

SDA INTERFACE

CX

EXC

CAPDAC

EXCITATION

THRESHOLD

AD7151

OUT

DIGITAL

OUTPUT

GND

Figure 20. AD7151 Block Diagram

The AD7151 core is a high performance capacitance-to-digital

converter (CDC) that allows the part to be interfaced directly to

a capacitive sensor.

The comparator compares the CDC result with thresholds, either

fixed or dynamically adjusted by the on-chip adaptive threshold

algorithm engine. Thus, the output indicates a defined change in

the input sensor capacitance.

The AD7151 also integrates an excitation source and CAPDAC

for the capacitive inputs, an input multiplexer, a complete clock

generator, a power-down timer, a power supply monitor, control

logic, and an I2C®-compatible serial interface for configuring the

part and accessing the internal CDC data and status, if required

in the system (see Figure 20).

CAPACITANCE-TO-DIGITAL CONVERTER

Figure 21 shows the CDC simplified functional diagram. The

converter consists of a second-order sigma delta (Σ-Δ), charge

balancing modulator and a third-order digital filter. The

measured capacitance CX is connected between an excitation

source and the Σ-Δ modulator input. The excitation signal is

applied on the CX during the conversion, and the modulator

continuously samples the charge going through the CX. The

digital filter processes the modulator output, which is a stream

of 0s and 1s containing the information in 0 and 1 density. The

data is processed by the adaptive threshold engine and output

comparators; the data can be also read through the serial interface.

The AD7151 is designed for floating capacitive sensors.

Therefore, both CX plates have to be isolated from ground or

any other fixed potential node in the system.

The AD7151 features slew rate limiting on the excitation voltage

output, which decreases the energy of higher harmonics on the

excitation signal and dramatically improves the system

electromagnetic compatibility (EMC).

CIN

CX

0pF TO 4pF

EXC

CAPACITANCE TO DIGITAL CONVERTER

(CDC)

CLOCK

GENERATOR

Σ-Δ

MODULATOR

0x000 TO 0xFFF

DATA

DIGITAL

FILTER

EXCITATION

Figure 21. CDC Simplified Block Diagram

CAPDAC

The AD7151 CDC core maximum full-scale input range is 4 pF.

However, the part can accept a higher capacitance on the input,

and the offset (nonchanging component) capacitance of up to 10

pF can be balanced by a programmable on-chip CAPDAC.

CIN

CSENS

10pF TO 14pF

EXC

CAPDAC

10pF

0x000 TO 0xFFF

DATA

0pF TO 4pF

CDC

Figure 22. Using CAPDAC

The CAPDAC can be understood as a negative capacitance

connected internally to the CIN pin. The CAPDAC has a 6-bit

resolution and a monotonic transfer function. Figure 22 shows

how to use the CAPDAC to shift the CDC 4 pF input range to

measure capacitance between 10 pF and 14 pF.

Rev. 0 | Page 10 of 28

11 Page | ||

| Páginas | Total 29 Páginas | |

| PDF Descargar | [ Datasheet AD7151.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AD7150 | Capacitance Converter | Analog Devices |

| AD7151 | Capacitance Converter | Analog Devices |

| AD7152 | 12-Bit Capacitance-to-Digital Converter | Analog Devices |

| AD7153 | 12-Bit Capacitance-to-Digital Converter | Analog Devices |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |