|

|

PDF LC709006A Data sheet ( Hoja de datos )

| Número de pieza | LC709006A | |

| Descripción | I/O-Expander for Microcontroller | |

| Fabricantes | ON Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de LC709006A (archivo pdf) en la parte inferior de esta página. Total 14 Páginas | ||

|

No Preview Available !

Ordering number : EN8265A

LC709006A

CMOS IC

I/O-Expander for Microcontroller

http://onsemi.com

Overview

The LC709006A is a peripheral IC dedicated for expanding the capability of the microcontroller (MCU) I/O ports.

It interfaces with the microcontroller through synchronous serial communication. Communication with the extended

I/O ports is accomplished through 24-bit parallel I/O. The extended port features include the capabilities to specify the

I/O direction on a bit basis, to specify the output type (CMOS or N-channel open drain), and to specify the I/O

voltage level on a port basis according to the power level of the peripheral equipment. These features make allow the

LC709004A to be used in a wide variety of applications.

Features

• 4-/5-wire synchronous serial transmission and reception, and 24-bit parallel I/O

• Wide operating voltage range (2.0V to 6.0V)

• Multifunction I/O ports

- I/O direction specification: Bit units

- CMOS or Nch-OD output type specification: Bit units

- Output voltage adjustment: Port (8 bits) units

• Output current: 12mA max. (capable of driving a green LED directly)

• Data transmission and reception: Can control reception of input data and transmission of output data in parallel.

• Cascaded configuration: Ports can be expanded in units of 24 bits × n (n is the number of LSI chips).

• Packaging from: MFP36SDJ (375mil): lead-free type

Semiconductor Components Industries, LLC, 2013

May, 2013

Ver.1.2

N0712HKIM B8-8713 No.8265-1/14

1 page

LC709006A

Switching I/O Characteristics at Ta=-40 to +85°C, VDD=VDDP0=VDDP1=VDDP2, VSS=VSSP0=VSSP1=VSSP2, VSS=0V

Parameter

Clock setup time

Symbol

TsCLK

Chip select low level setup TslCS

time

Chip select low level hold ThlCS

time

Clock hold time

ThCLK

Clock low level pulse width TwlCLK

Pin/Remarks

Conditions

CS, CLK

CS, CLK

CS, CLK

CS, CLK

CLK

•Specified with

respect to falling

edge of CS.

•See Fig. 9.

•Specified with

respect to falling

edge of CS.

•See Fig. 9.

•Specified with

respect to falling

edge of CS.

•See Fig. 9.

•Specified with

respect to falling

edge of CS.

•See Fig. 9.

•See Fig. 9.

VDD[V]

2.0 to 6.0

2.0 to 6.0

2.0 to 6.0

2.0 to 6.0

4.5 to 6.0

Specification

min typ max

100

100

100

200

250

Unit

2.7 to 6.0

500

2.0 to 6.0

1000

Clock high level pulse

width

TwhCLK CLK

•See Fig. 9.

4.5 to 6.0

2.7 to 6.0

250

500

2.0 to 6.0

1000

Chip select high level

setup time

Chip select high level hold

time

Chip select low level pulse

width

Reset low level pulse width

TshCS

ThhCS

TwlCS

TwlRES

CS, RES

CS, RES

CS, RES

CS, RES

•See Fig. 9.

•See Fig. 9.

•See Fig. 9.

•See Fig. 9.

2.0 to 6.0

2.0 to 6.0

2.0 to 6.0

2.0 to 6.0

200

100

200

150

ns

Data setup time

Data hold time

TsDIN

DIN

ThDIN

DIN

•Specified with

respect to falling

edge of CLK.

•See Fig. 9.

•Specified with

respect to falling

edge of CLK.

•See Fig. 9.

4.5 to 6.0

2.0 to 6.0

4.5 to 6.0

2.7 to 6.0

2.0 to 6.0

30

50

50

150

300

Serial data output delay

time

(Note 4)

TdD0UT DOUT

•Specified with

respect to falling

edge of CLK.

•See Fig. 9.

4.5 to 6.0

2.7 to 6.0

2.0 to 6.0

200

400

800

Port data output delay time TdPOUT Port 0 to 2

•Specified with

respect to rising

edge of CS.

•See Fig. 9.

4.5 to 6.0

2.7 to 6.0

2.0 to 6.0

200

400

800

Port data input setup time TsPIN

Port 0 to 2

•Specified with

respect to rising

4.5 to 6.0

30

edge of CLK.

•See Fig. 9.

2.0 to 6.0

50

Port data input hold time

ThPIN

Port 0 to 2

•Specified with

respect to rising

edge of CLK.

•See Fig. 9.

4.5 to 6.0

2.7 to 6.0

2.0 to 6.0

50

150

300

Note 4: The input data of P00 will be out from DOUT terminal at the first negative edge of CLK signal. Because of this,

Serial data output delay time of the first clock will be the time measured from the negative edge of the CLK or

the time at the input data (P00) is settled.

No.8265-5/14

5 Page

LC709006A

Application Examples

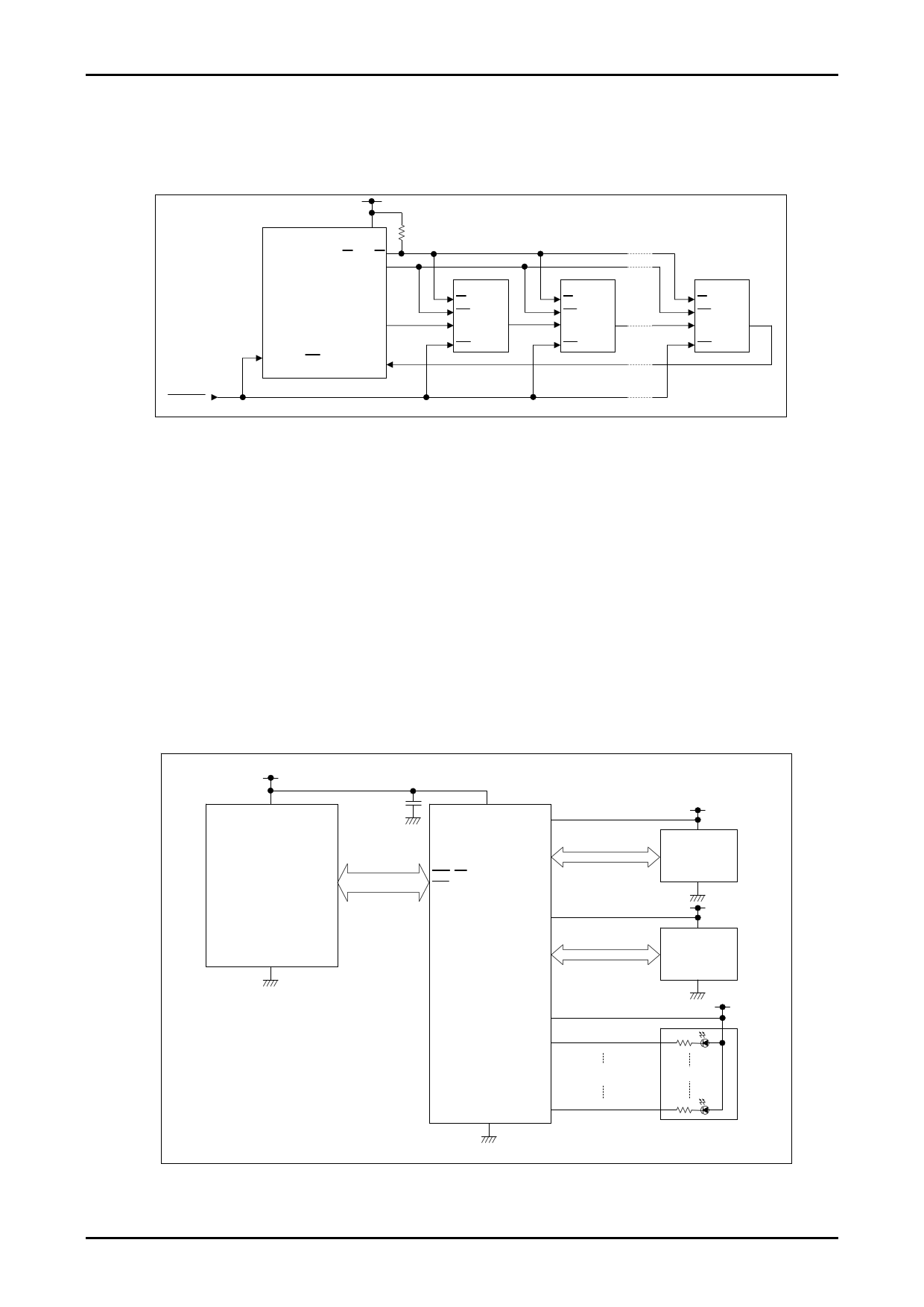

(1) Example of a cascade configuration

Two or more LC709006A LSI chips can be cascaded to realize port expansion beyond 24 bits. Port expansion,

however, need to be made in units of 24 bits × n (n denotes the number of LSI chips).

System Reset

VDD

Microcontroller(MCU)

Serial CS Output(CS)

Serial Clock Output(SCK)

Serial Data Output(SDO)

System Reset(RES)

Serial Data Input(SDI)

LC709006

CS

CLK

DIN DOUT

RES (LSI=1)

LC709006

CS

CLK

DIN DOUT

RES

(LSI=2)

LC709006

CS

CLK

DIN DOUT

RES

(LSI=n)

Fig. 5

(2) Variable port power level example

When controlling the level of I/O ports according to the power voltage level of the peripheral equipment, the user

can connect the output from the power supply of the peripheral equipment directly to the power supply pins for the

I/O ports. The LC709006A dispenses with the need to add an external level shifter circuit.

Note the following when configuring the LC709006A in this way:

Note 5:

• VDDP0: The voltage level of VDDP0 must not be higher than that of VDD (VDDP0≤VDD).

• VDDP1: The voltage level of VDDP1 must not be lower than that of VDD (VDDP1≥VDD).

• VDDP2: The voltage level of VDDP2 must not be lower than that of VDD (VDDP2≥VDD).

• The input level of all ports (P00 to P27) is dependent on the VDD power source; it depends on none of the power

sources VDDP0 to VDDP2.

* Be sure to check the electrical characteristics of the LC709006A.

3.3V

VDD

Microcontroller(MCU)

VSS

0.1μF

VDD

VDDP0

RES, CE,

3.3V serial send/receive CLK, DIN, DOUT

P00 to P07

2.5V parallel data I/O

VDDP1

LC709006

P10 to P17

5V parallel data I/O

2.5V

2.5V peripheral

5V

5V peripheral

VDDP2

5V

P20 to P27

Nch-open drain display

data output

LED display

VSS, VSSP0, VSSP2

Fig. 6

No.8265-11/14

11 Page | ||

| Páginas | Total 14 Páginas | |

| PDF Descargar | [ Datasheet LC709006A.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| LC709006A | I/O-Expander for Microcontroller | ON Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |