|

|

PDF GD25Q128C Data sheet ( Hoja de datos )

| Número de pieza | GD25Q128C | |

| Descripción | 3.3V Uniform Sector Dual and Quad Serial Flash | |

| Fabricantes | ELM | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de GD25Q128C (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

http://www.elm-tech.com

GD25Q128C

DATASHEET

1 page

GD25Q128CxIGx 3.3V Uniform Sector Dual and Quad Serial Flash

2. GENERAL DESCRIPTION

http://www.elm-tech.com

The GD25Q128C(128M-bit) Serial flash supports the standard Serial Peripheral Interface (SPI), and supports

the Dual/Quad SPI: Serial Clock, Chip Select, Serial Data I/O0 (SI), I/O1 (SO), I/O2 (WP#) and I/O3 (HOLD#/

RESET#). The Dual I/O data is transferred with speed of 208Mbits/s and the Quad I/O & Quad Output data is

transferred with speed of 320Mbits/s.

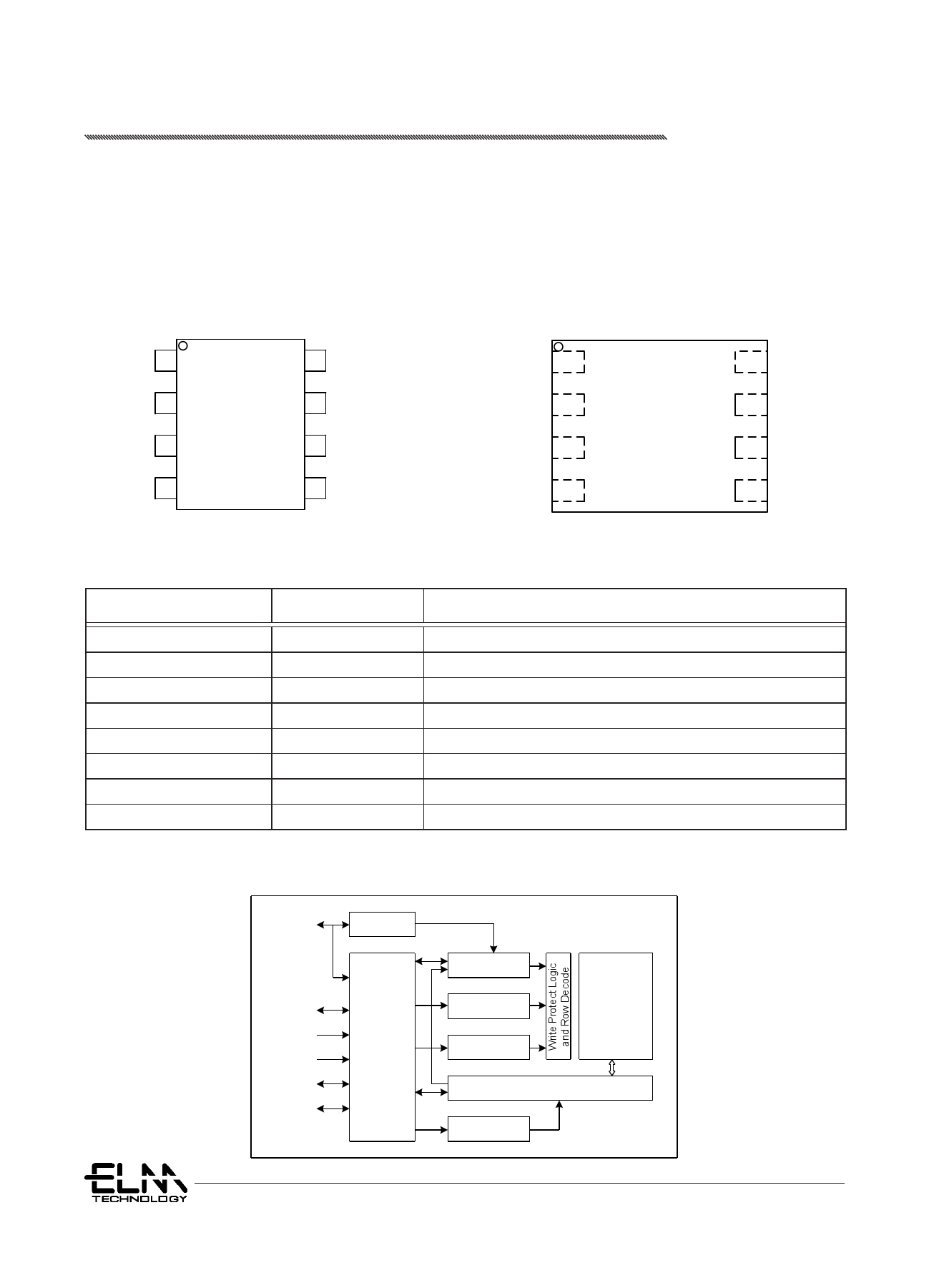

Connection Diagram

CS# 1

8

SO

WP#

27

Top View

36

VSS 4

5

88–-LLEEAADD SSOOPP

Pin Description

Pin Name

CS#

SO (IO1)

WP# (IO2)

VSS

SI (IO0)

SCLK

HOLD#/RESET (IO3)

VCC

VCC

HOLD#/

RESET#

SCLK

SI

I/O

I

I/O

I/O

I/O

I

I/O

CS# 1

SO 2

WP# 3

VSS 4

Top View

88-L–ELAEADDWWSSOONN

8 VCC

7

HOLD#/

RESET#

6 SCLK

5 SI

Description

Chip Select Input

Data Output (Data Input Output 1)

Write Protect Input (Data Input Output 2)

Ground

Data Input (Data Input Output 0)

Serial Clock Input

Hold or Reset Input (Data Input Output 3)

Power Supply

Block Diagram

WP#(IO2)

Write Control

Logic

HOLD#

RESET#(IO3)

SCLK

CS#

SI(IO0)

SO(IO1)

SPI

Command &

Control Logic

Status

Register

High Voltage

Generators

Flash

Memory

Page Address

Latch/Counter

Column Decode And

256-Byte Page Buffer

Byte Address

Latch/Counter

69 - 5

Rev.1.2

5 Page

GD25Q128CxIGx 3.3V Uniform Sector Dual and Quad Serial Flash

6. STATUS REGISTER

http://www.elm-tech.com

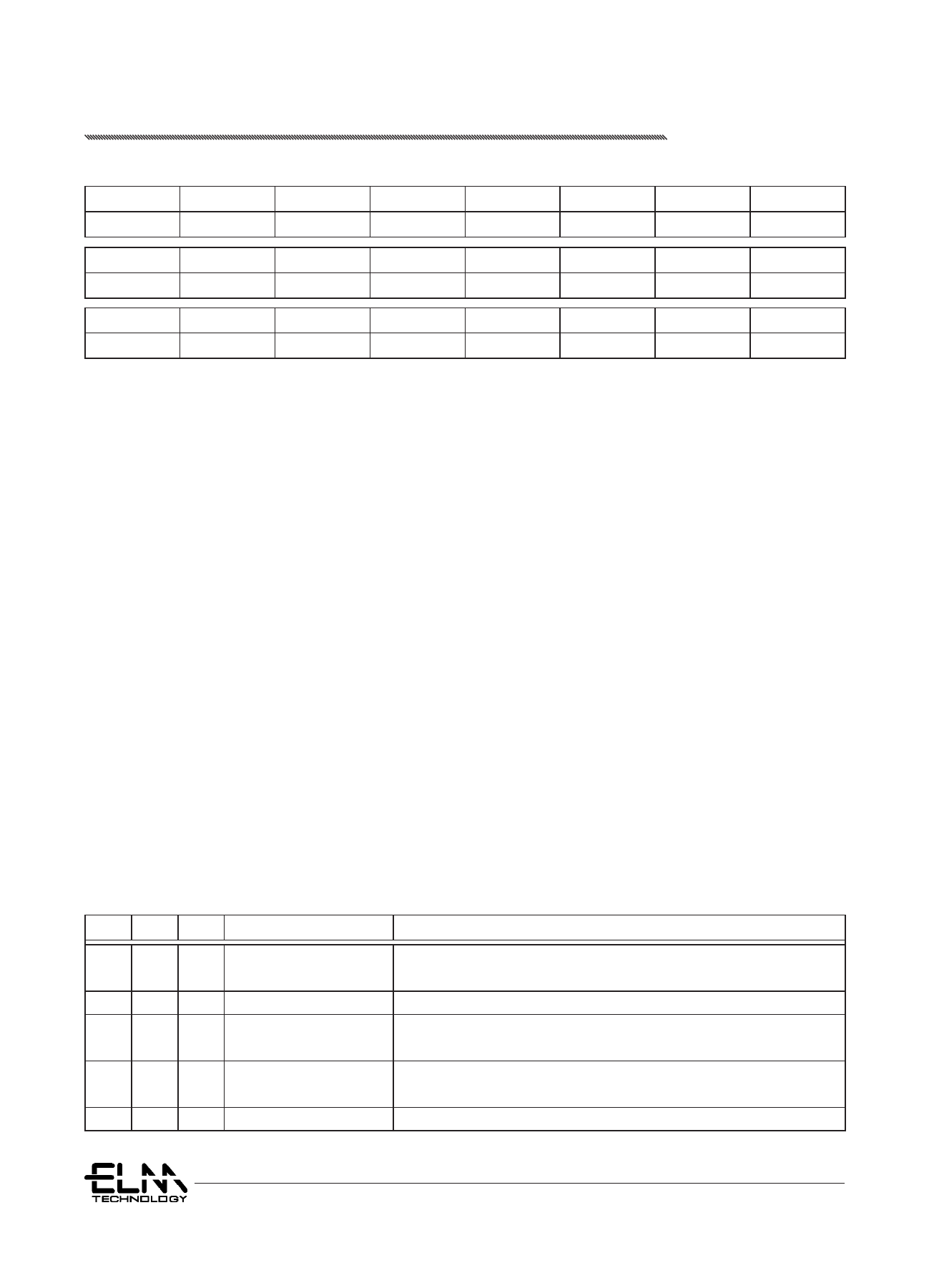

S23

HOLD/RST

S22

DRV1

S21

DRV0

S20

Reserved

S19

Reserved

S18

WPS

S17

Reserved

S16

Reserved

S15 S14 S13 S12 S11 S10

S9

S8

SUS1

CMP

LB3

LB2

LB1 SUS2

QE

SRP1

S7 S6 S5 S4 S3 S2 S1 S0

SRP0

BP4

BP3

BP2

BP1

BP0 WEL WIP

The status and control bits of the Status Register are as follows:

WIP bit.

The Write in Progress (WIP) bit indicates whether the memory is busy in program/erase/write status register

progress. When WIP bit sets to 1, means the device is busy in program/erase/write status register progress, when

WIP bit sets 0, means the device is not in program/erase/write status register progress.

WEL bit.

The Write Enable Latch (WEL) bit indicates the status of the internal Write Enable Latch. When set to 1 the

internal Write Enable Latch is set, when set to 0 the internal Write Enable Latch is reset and no Write Status

Register, Program or Erase command is accepted.

BP4, BP3, BP2, BP1, BP0 bits.

The Block Protect (BP4, BP3, BP2, BP1 and BP0) bits are non-volatile. They define the size of the area to be

software protected against Program and Erase commands. These bits are written with the Write Status Register

(WRSR) command. When the Block Protect (BP4, BP3, BP2, BP1 and BP0) bits are set to 1, the relevant

memory area (as defined in Table1). becomes protected against Page Program (PP), Sector Erase (SE) and Block

Erase (BE) commands. The Block Protect (BP4, BP3, BP2, BP1 and BP0) bits can be written provided that

the Hardware Protected mode has not been set. The Chip Erase (CE) command is executed, only if the Block

Protect (BP2, BP1 and BP0) bits are 0 and CMP=0.

SRP1, SRP0 bits.

The Status Register Protect (SRP1 and SRP0) bits are non-volatile Read/Write bits in the status register. The

SRP bits control the method of write protection: software protection, hardware protection, power supply lock-

down or one time programmable protection.

SRP1 SRP0 #WP Status Register

Description

0

0

×

Software Protected

The Status Register can be written to after a Write Enable

command, WEL=1.(Default)

0 1 0 Hardware Protected WP#=0, the Status Register locked and can not be written to.

0

1

1

Hardware Unprotected

WP#=1, the Status Register is unlocked and can be written to

after a Write Enable command, WEL=1.

10×

Power Supply

Lock-Down(1)

Status Register is protected and can not be written to again until

the next Power-Down, Power-Up cycle.

1 1 × One Time Program(2) Status Register is permanently protected and can not be written to.

NOTE: (1). When SRP1, SRP0= (1, 0), a Power-Down, Power-Up cycle will change SRP1, SRP0 to (0, 0) state.

(2). This feature is available on special order. Please contact ELM for details.

69 - 11

Rev.1.2

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet GD25Q128C.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| GD25Q128 | Uniform sector dual and quad serial flash | ELM |

| GD25Q128B | Uniform sector dual and quad serial flash | ELM |

| GD25Q128B | Dual and Quad Serial Flash | GigaDevice |

| GD25Q128BxIGx | Uniform sector dual and quad serial flash | ELM |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |