|

|

PDF HD74HC194 Data sheet ( Hoja de datos )

| Número de pieza | HD74HC194 | |

| Descripción | 4-bit Bidirectional Universal Shift Register | |

| Fabricantes | Renesas | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de HD74HC194 (archivo pdf) en la parte inferior de esta página. Total 9 Páginas | ||

|

No Preview Available !

HD74HC194

4-bit Bidirectional Universal Shift Register

REJ03D0589–0200

(Previous ADE-205-466)

Rev.2.00

Jan 31, 2006

Description

This bidirectional shift register is designed to incorporate virtually all of the features a system designer may want in a

shift register. It features parallel inputs, parallel outputs, right shift and left shift serial inputs, operating mode control

inputs, and a direct overriding clear line. The register has four distinct modes of operation: parallel (broadside) load,

shift right (in the direction QA toware QD); shift left; inhibit clock (do nothing).

Synchronous parallel loading is accomplished by applying the four bits of data and taking both mode control inputs, S0

and S1, high. The data are loaded into their respective flip-flops and appear at the outputs after the positive transition of

the clock input. During loading, serial data flow is inhibited. Shift right is accomplished synchronously with the rising

edge of the clock pulse when S0 is high and S1 is low. Serial data for this mode is entered at the shift right data input.

When S0 is low and S1 is high, data shifts left synchronously and new data is entered at the shift left serial input.

Clocking of the flip-flops is inhibited when both mode control inputs are low. The mode control inputs should be

changed only when the clock input is high.

Features

• High Speed Operation: tpd (Clock to Q) = 12 ns typ (CL = 50 pF)

• High Output Current: Fanout of 10 LSTTL Loads

• Wide Operating Voltage: VCC = 2 to 6 V

• Low Input Current: 1 µA max

• Low Quiescent Supply Current: ICC (static) = 4 µA max

• Ordering Information

Part Name

Package Type

Package Code

(Previous Code)

Package

Abbreviation

HD74HC194P

DILP-16 pin

PRDP0016AE-B

(DP-16FV)

P

Taping Abbreviation

(Quantity)

—

Rev.2.00 Jan 31, 2006 page 1 of 8

1 page

HD74HC194

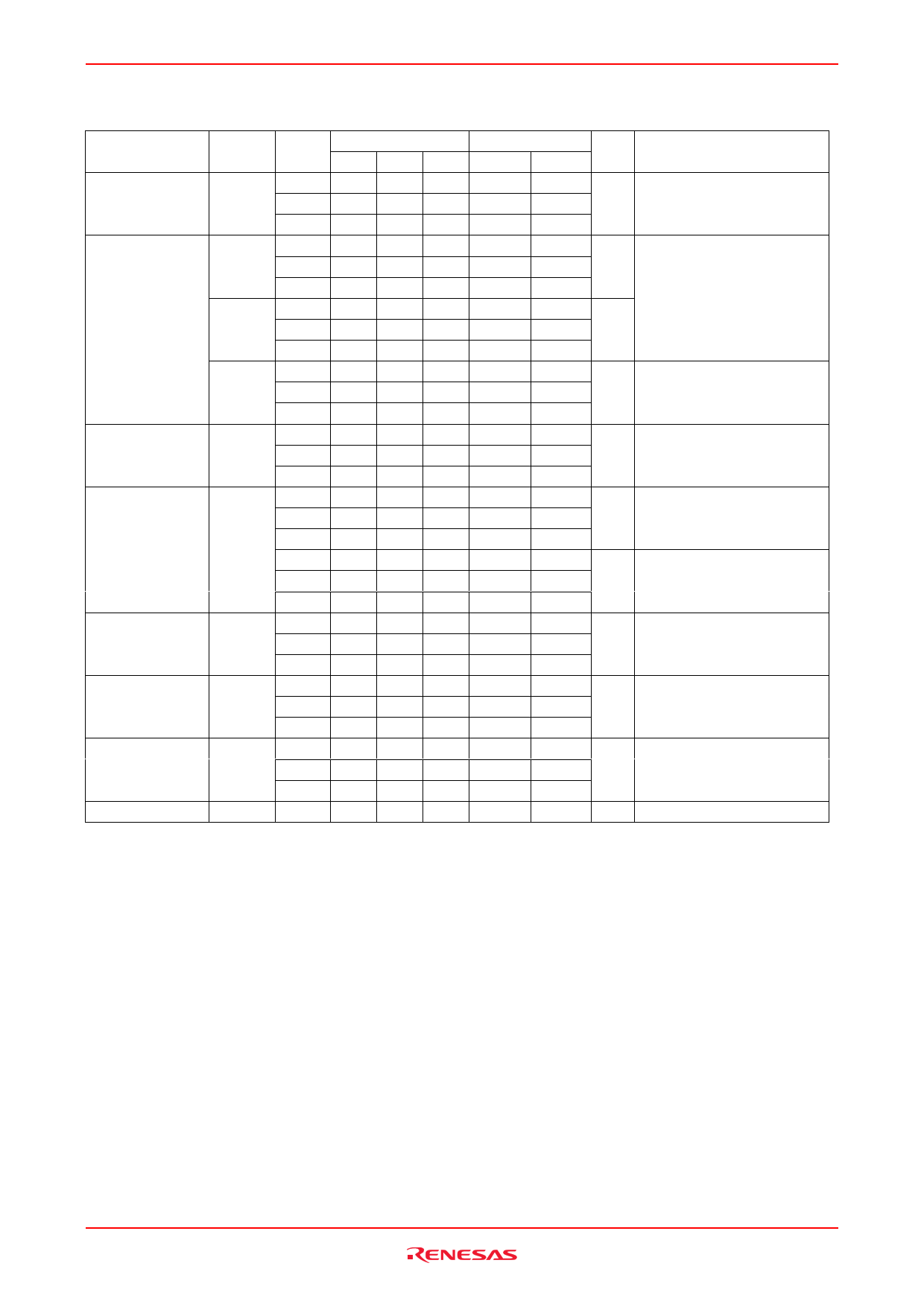

Switching Characteristics

Item

Maximum clock

frequency

Propagation delay

time

Pulse width

Setup time

Hold time

Removal time

Output rise/fall

time

Input capacitance

Symbol VCC (V)

fmax 2.0

4.5

6.0

tPHL 2.0

4.5

6.0

tPLH 2.0

4.5

6.0

tPHL 2.0

4.5

6.0

tw 2.0

4.5

6.0

tsu 2.0

4.5

6.0

2.0

4.5

6.0

th 2.0

4.5

6.0

trem 2.0

4.5

6.0

tTLH 2.0

tTHL 4.5

6.0

Cin —

(CL = 50 pF, Input tr = tf = 6 ns)

Ta = 25°C

Ta = –40 to +85°C

Unit

Min Typ Max Min Max

Test Conditions

—— 6

—

5 ns

— — 30

—

24

— — 35

—

28

— — 140 —

175 ns Clock to Q

— 12 28

—

35

— — 24

—

30

— — 140 —

175 ns

— 12 28

—

35

— — 24

—

30

— — 150 —

190 ns Clear to Q

— 13 30

—

38

— — 26

—

33

80 — — 100

— ns Clock or Clear

16 6 —

20

—

14 — —

17

—

100 — — 125

— ns A, B, C or D to Clock

20 7 —

25

—

17 — —

21

—

150 — — 187

— ns Mode controls to Clock

30 17 —

37

—

25 — —

31

—

0 ——

0

— ns Any input

0 –4 —

0

—

0 ——

0

—

25 — —

31

— ns Clear inactive to Clock

5 1—

6

—

4 ——

5

—

— — 75

—

95 ns

— 5 15

—

19

— — 13

—

16

— 5 10

—

10 pF

Rev.2.00 Jan 31, 2006 page 5 of 8

5 Page | ||

| Páginas | Total 9 Páginas | |

| PDF Descargar | [ Datasheet HD74HC194.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| HD74HC190 | Synchronous Up/Down Decade/4-bit Binary Counter(Single Clock Line) | Hitachi Semiconductor |

| HD74HC191 | Synchronous Up/Down Decade/4-bit Binary Counter(Single Clock Line) | Hitachi Semiconductor |

| HD74HC192 | Synchronous Up/Down Decade/4-bit Binary Counter(Dual Clock Line) | Hitachi Semiconductor |

| HD74HC193 | Synchronous Up/Down Decade/4-bit Binary Counter(Dual Clock Line) | Hitachi Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |