|

|

PDF K4N56163QG Data sheet ( Hoja de datos )

| Número de pieza | K4N56163QG | |

| Descripción | 256Mbit gDDR2 SDRAM | |

| Fabricantes | Samsung | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de K4N56163QG (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

K4N56163QG

256M gDDR2 SDRAM

256Mbit gDDR2 SDRAM

Revision 1.4

December 2006

Notice

INFORMATION IN THIS DOCUMENT IS PROVIDED IN RELATION TO SAMSUNG PRODUCTS,

AND IS SUBJECT TO CHANGE WITHOUT NOTICE.

NOTHING IN THIS DOCUMENT SHALL BE CONSTRUED AS GRANTING ANY LICENSE,

EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE,

TO ANY INTELLECTUAL PROPERTY RIGHTS IN SAMSUNG PRODUCTS OR TECHNOLOGY. ALL

INFORMATION IN THIS DOCUMENT IS PROVIDED

ON AS "AS IS" BASIS WITHOUT GUARANTEE OR WARRANTY OF ANY KIND.

1. For updates or additional information about Samsung products, contact your nearest Samsung office.

2. Samsung products are not intended for use in life support, critical care, medical, safety equipment, or similar

applications where Product failure could result in loss of life or personal or physical harm, or any military or

defense application, or any governmental procurement to which special terms or provisions may apply.

* Samsung Electronics reserves the right to change products or specification without notice.

- 1/64 -

Rev. 1.4 Dec. 2006

1 page

K4N56163QG

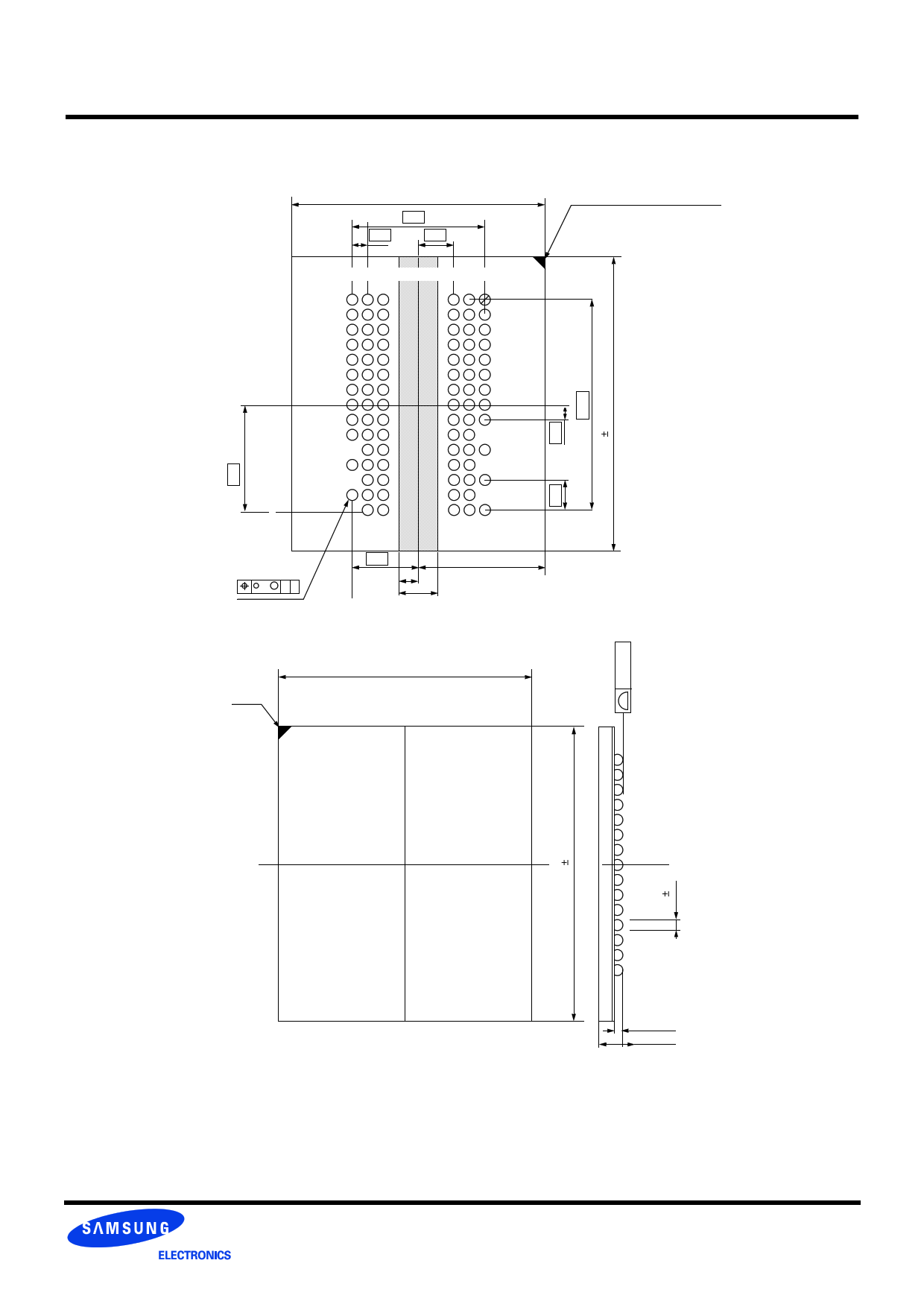

5.0 PACKAGE DIMENSIONS (84 Ball FBGA)

11.00 ± 0.10

6.40

0.80 1.60

987654321

A

B

C

D

E

F

G

H

J

K

L

M

N

P

R

84-∅0.45±0.05

∅0.2 M A B

3.20

(0.90)

(1.80)

(5.5)

256M gDDR2 SDRAM

# A1 INDEX MARK (OPTIONAL)

11.00 ± 0.10

#A1

- 5/64 -

0.35±0.05

MAX.1.20

Unit : mm

Rev. 1.4 Dec. 2006

5 Page

K4N56163QG

256M gDDR2 SDRAM

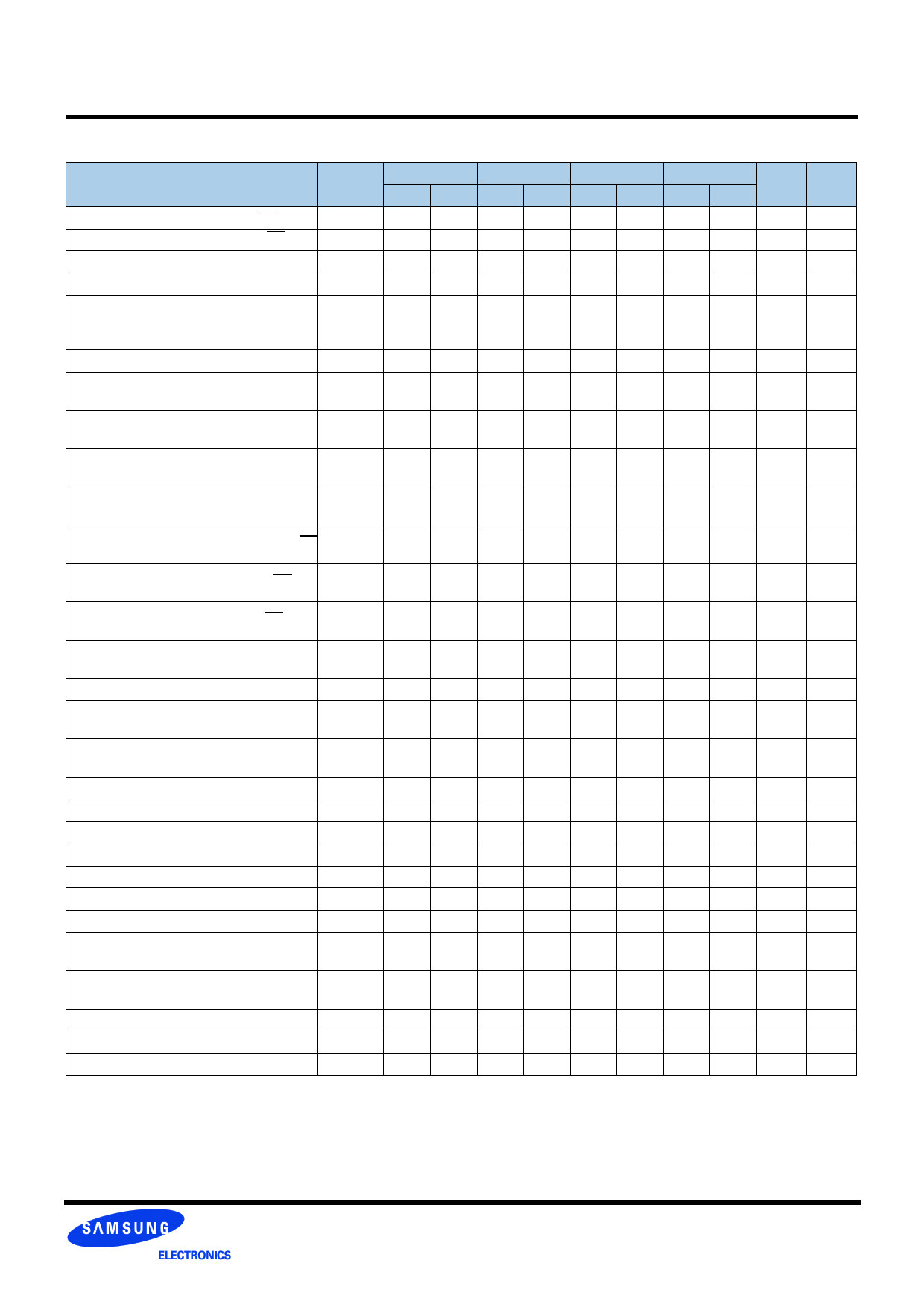

9.3 Timing Parameters by Speed Grade

(Refer to notes for informations related to this table at the bottom)

Parameter

- 20 - 22 - 25 - 2A

Symbol

Units Notes

min max min max min max min max

DQ output access time from CK/CK

tAC -350 +350 -350 +350 -400 +400 -450 +450 ps

DQS output access time from CK/CK

tDQSCK -300 +300 -300 +300 -350 +350 -400 +400 ps

CK high-level width

tCH 0.45 0.55 0.45 0.55 0.45 0.55 0.45 0.55 tCK

CK low-level width

tCL 0.45 0.55 0.45 0.55 0.45 0.55 0.45 0.55 tCK

CK half period

min min min min

tHP (tCL, x (tCL, x (tCL, x (tCL, x

tCH)

tCH)

tCH)

tCH)

ps 20,21

Clock cycle time, CL= x

tCK 2.0 8.0 2.2 8.0 2.5 8.0 2.86 8.0 ns 24

DQ and DM input hold time

tDH 175 x 175 x 175

x 175

x

ps

15,16,

17

DQ and DM input setup time

tDS

50

x 50

x 50

x 50

x

ps

15,16,

17

Control & Address input pulse width for

each input

tIPW 0.6 x 0.6 x 0.6 x 0.6 x tCK

DQ and DM input pulse width for each

input

tDIPW 0.35 x 0.35 x 0.35 x 0.35 x tCK

Data-out high-impedance time from CK/CK tHZ

x

tAC

max

x

tAC

max

x

tAC

max

x

tAC

max

ps

DQS low-impedance time from CK/CK

tLZ

(DQS)

tAC tAC tAC tAC tAC tAC tAC tAC

min max min max min max min max

ps

27

DQ low-impedance time from CK/CK

tLZ(DQ)

2*tAC

min

tAC

max

2*tAC

min

tAC

max

2*tAC

min

tAC

max

2*tAC

min

tAC

max

ps

27

DQS-DQ skew for DQS and associated

DQ signals

tDQSQ

x 280

x 280

x 280

x 310 ps

22

DQ hold skew factor

tQHS

x 380

x 380

x 380

x 410 ps

21

DQ/DQS output hold time from DQS

tQH

tHP -

tQHS

x

tHP -

tQHS

x

tHP -

tQHS

x

tHP -

tQHS

x

ps

Write command to first DQS latching tran-

sition

tDQSS

WL WL WL WL WL WL WL WL

-0.25 +0.25 -0.25 +0.25 -0.25 +0.25 -0.25 +0.25

tCK

DQS input high pulse width

tDQSH 0.35 x 0.35 x 0.35 x 0.35 x tCK

DQS input low pulse width

tDQSL 0.35 x 0.35 x 0.35 x 0.35 x tCK

DQS falling edge to CK setup time

tDSS 0.2

x 0.2

x 0.2

x 0.2

x tCK

DQS falling edge hold time from CK

tDSH 0.2

x 0.2

x 0.2

x 0.2

x tCK

Mode register set command cycle time

tMRD

2

x2

x2

x2

x tCK

Write postamble

tWPST 0.4 0.6 0.4 0.6 0.4 0.6 0.4 0.6 tCK 19

Write preamble

tWPRE 0.35 x 0.35 x 0.35 x 0.35 x tCK

Address and control input hold time

tIH

200 x 200 x 250 x 325

x

ps

14,16,

18

Address and control input setup time

tIS

150 x 150 x 175 x 200 x

ps

14,16,

18

Read preamble

tRPRE 0.9 1.1 0.9 1.1 0.9 1.1 0.9 1.1 tCK 28

Read postamble

tRPST 0.4 0.6 0.4 0.6 0.4 0.6 0.4 0.6 tCK 28

Active to active command period

tRRD 7.5 x 7.5 x 7.5 x 7.5 x ns 12

- 11/64 -

Rev. 1.4 Dec. 2006

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet K4N56163QG.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| K4N56163QF-GC | 256Mbit gDDR2 SDRAM | Samsung |

| K4N56163QG | 256Mbit gDDR2 SDRAM | Samsung |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |