|

|

PDF IS46LD32160A Data sheet ( Hoja de datos )

| Número de pieza | IS46LD32160A | |

| Descripción | 512Mb Mobile LPDDR2 S4 SDRAM | |

| Fabricantes | ISSI | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de IS46LD32160A (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

IS43/46LD16320A

IS43/46LD32160A

512Mb (x16, x32) Mobile LPDDR2 S4 SDRAM

FEATURES

• Low-voltage Core and I/O Power Supplies

VDD2 = 1.14-1.30V, VDDCA/VDDQ = 1.14-1.30V,

VDD1 = 1.70-1.95V

• High Speed Un-terminated Logic(HSUL_12) I/O

Interface

• Clock Frequency Range : 10MHz to 533MHz

(data rate range : 20Mbps to 1066Mbps per I/O)

• Four-bit Pre-fetch DDR Architecture

• Multiplexed, double data rate, command/ad-

dress inputs

• Four internal banks for concurrent operation

• Bidirectional/differential data strobe per byte of

data (DQS/DQS#)

• Programmable Read/Write latencies(RL/WL)

and burst lengths(4,8 or 16)

• ZQ Calibration

• On-chip temperature sensor to control self re-

fresh rate

• Partial –array self refresh(PASR)

• Deep power-down mode(DPD)

• Operation Temperature

Commercial (TC = 0°C to 85°C)

Industrial (TC = -40°C to 85°C)

Automotive, A1 (TC = -40°C to 85°C)

Automotive, A2 (TC = -40°C to 105°C)

OPTIONS

• Configuration:

− 32Mx16 (8M x 16 x 4 banks)

− 16Mx32 (4M x 32 x 4 banks)

Package:

− 134-ball BGA for x16 / x32

− 168-ball PoP BGA for x32

DESCRIPTION

MAY 2016

The IS43/46LD16320A/32160A is 512Mbit CMOS

LPDDR2 DRAM. The device is organized as 4 banks

of 8Meg words of 16bits or 4Meg words of 32bits.

This product uses a double-data-rate architecture to

achieve high-speed operation. The double data rate

architecture is essentially a 4N prefetch architecture

with an interface designed to transfer two data words

per clock cycle at the I/O pins. This product offers fully

synchronous operations referenced to both rising and

falling edges of the clock. The data paths are internally

pipelined and 4n bits prefetched to achieve very high

bandwidth.

ADDRESS TABLE

Parameter

Row Addresses

Column Addresses

Bank Addresses

Refresh Count

16Mx32

R0-R12

C0-C8

BA0-BA1

4096

32Mx16

R0-R12

C0-C9

BA0-BA1

4096

KEY TIMING PARAMETERS(1)

Speed

Grade

-18

Data

Rate

(Mb/s)

1066

Write Read tRCD/

Latency Latency tRP(2)

4 8 Typical

-25 800

3

6 Typical

-3 667 2

5 Typical

Notes:

1. Other clock frequencies/data rates supported; please

refer to AC timing tables.

2. Please contact ISSI for Fast trcd/trp.

Copyright © 2016 Integrated Silicon Solution, Inc. All rights reserved. ISSI reserves the right to make changes to this specification and its products at any time without notice. ISSI assumes no

liability arising out of the application or use of any information, products or services described herein. Customers are advised to obtain the latest version of this device specification before relying on

any published information and before placing orders for products.

Integrated Silicon Solution, Inc. does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be ex-

pected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless Integrated Silicon

Solution, Inc. receives written assurance to its satisfaction, that:

a.) the risk of injury or damage has been minimized;

b.) the user assume all such risks; and

c.) potential liability of Integrated Silicon Solution, Inc is adequately protected under the circumstances

Integrated Silicon Solution, Inc. — www.issi.com 1

Rev. A

05/02/2016

1 page

IS43/46LD16320A

IS43/46LD32160A

INPUT/OUTPUT FUNCTIONAL DESCRIPTION

Pad Definition and Description

Name

CK, CK#

Type

Input

CKE

Input

CS# Input

CA0 - CA9 Input

DQ0 - DQ15

(x16)

DQ0 - DQ31

(x32)

I/O

Description

Clock: CK and CK# are differential clock inputs. All Double Data Rate (DDR) CA

inputs are sampled on both positive and negative edge of CK. Single Data Rate (SDR)

inputs, CS# and CKE, are sampled at the positive Clock edge.

Clock is defined as the differential pair, CK and CK#. The positive Clock edge is

defined by the crosspoint of a rising CK and a falling CK#. The negative Clock edge is

defined by the crosspoint of a falling CK and a rising CK#.

Clock Enable: CKE HIGH activates and CKE LOW deactivates internal clock signals and

therefore device input buffers and output drivers. Power savings modes are entered and

exited through CKE transitions.

CKE is considered part of the command code. See Command Truth Table for command

code descriptions.

CKE is sampled at the positive Clock edge.

Chip Select: CS# is considered part of the command code. See Command Truth Table

for command code descriptions.

CS# is sampled at the positive Clock edge.

DDR Command/Address Inputs: Uni-directional command/address bus inputs.

CA is considered part of the command code. See Command Truth Table for command

code descriptions.

Data Inputs/Output: Bi-directional data bus

I/O Data Strobe (Bi-directional, Differential): The data strobe is bi-directional (used for

DQS0,

DQS0#,

read and write data) and differential (DQS and DQS#). It is output with read data and

input with write data. DQS is edge-aligned to read data and centered with write data.

DQS1,

DQS1#

(x16)

DQS0 -

DQS3,

DQS0# -

DQS3#

For x16, DQS0 and DQS0# correspond to the data on DQ0 - DQ7; DQS1 and

DQS1# to the data on DQ8 - DQ15.

For x32 DQS0 and DQS0# correspond to the data on DQ0 - DQ7, DQS1 and

DQS1# to the data on DQ8 - DQ15, DQS2 and DQS2# to the data on DQ16 - DQ23,

DQS3 and DQS3# to the data on DQ24 - DQ31.

(x32)

Input

DM0-DM1

(x16)

DM0 - DM3

(x32)

Input Data Mask: For LPDDR2 devices that do not support the DNV feature, DM is the

input mask signal for write data. Input data is masked when DM is sampled HIGH

coincident with that input data during a Write access. DM is sampled on both edges of

DQS. Although DM is for input only, the DM loading shall match the DQ and DQS (or

DQS#).

DM0 is the input data mask signal for the data on DQ0-7.

For x16 and x32 devices, DM1 is the input data mask signal for the data on DQ8-15.

For x32 devices, DM2 is the input data mask signal for the data on DQ16-23 and DM3 is

the input data mask signal for the data on DQ24-31.

Integrated Silicon Solution, Inc. — www.issi.com 5

Rev. A

05/02/2016

5 Page

IS43/46LD16320A

IS43/46LD32160A

5. ZQ Calibration

After tINIT5 (Tf ), the MRR initialization calibration (ZQ_CAL) command can be issued to the memory (MR10).

This command is used to calibrate output impedance over process, voltage, and temperature. In systems where more

than one LPDDR2 device exists on the same bus, the controller must not overlap MRR ZQ_CAL commands. The

device is ready for normal operation after tZQINIT.

6. Normal Operation

After tZQINIT (Tg), MRW commands must be used to properly configure the memory . Specifically, MR1, MR2, and

MR3 must be set to configure the memory for the target frequency and memory configuration

After the initialization sequence is complete, the device is ready for any valid command. After Tg, the clock frequency

can be changed using the procedure described in Input Clock Frequency Changes and Clock Stop Events‖.

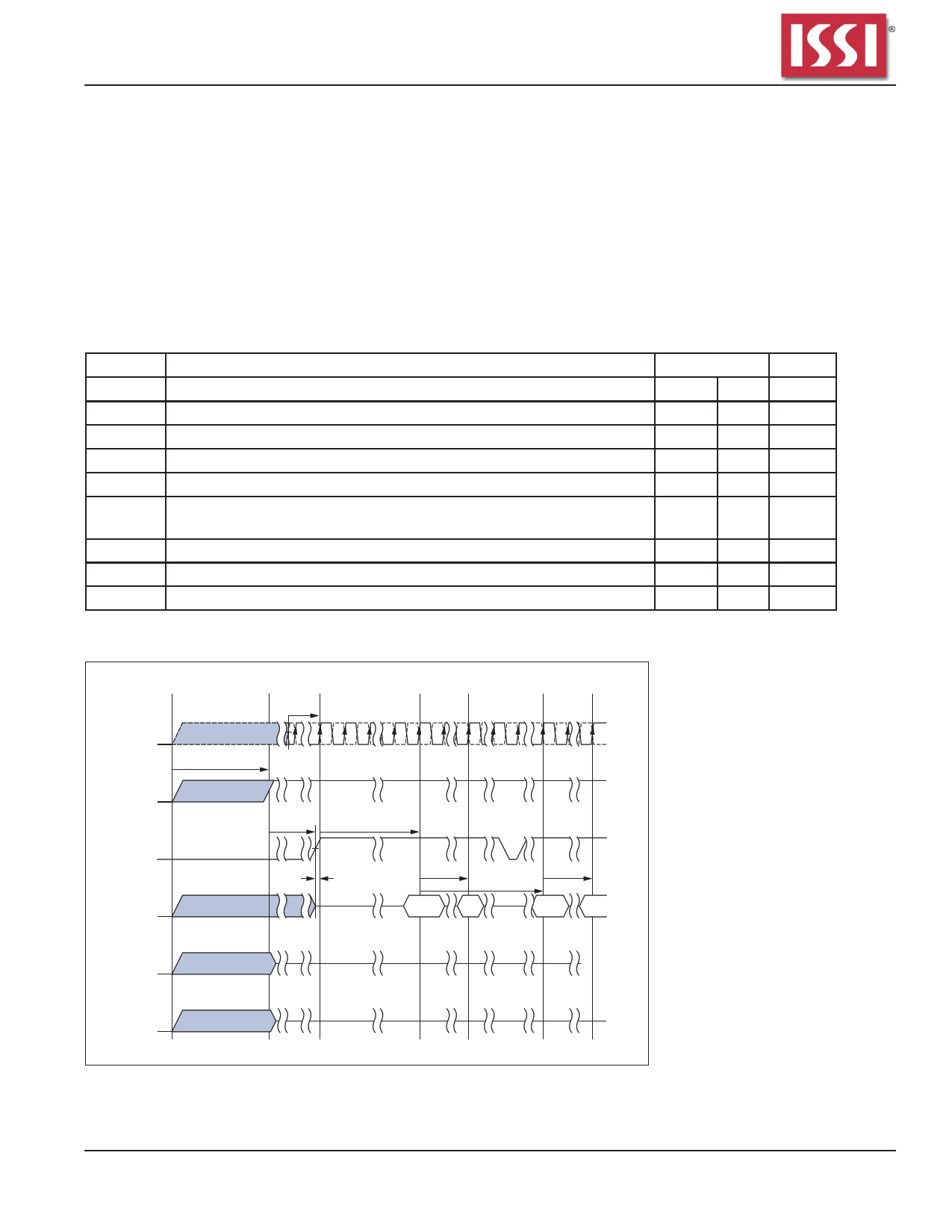

INITIALIZATION TIMING

Symbol Parameter

tINIT0

tINIT1

tINIT2

tINIT3

tINIT4

tINIT5

tCKb

tZQINIT

Maximum Power Ramp Time

Minimum CKE low time after completion of power ramp

Minimum stable clock before first CKE high

Minimum idle time after first CKE assertion

Minimum idle time after Reset command, this time will be about 2 x

tRFCab + tRPab

Maximum duration of Device Auto-Initialization

Clock cycle time during boot

ZQ initial calibration

Value

min max

- 20

100 -

5-

200 -

1-

Unit

ms

ns

tCK

us

us

- 10 us

18 100 ns

1 - us

Figure - Power Ramp and Initialization Sequence

Ta

CK/CK#

Supplies

tINIT0

CKE

CA

Tb Tc

tINIT2

Td Te

tINIT1

tINIT3

tISCKE

tINIT4

tINIT5

RESET MRR

Tf Tg

tZQINIT

MRW

ZQ_CAL

Valid

R TT

DQ

Initialization After RESET (without voltage ramp):

If the RESET command is issued before or after the power-up initialization sequence, the re-initialization procedure

must begin at Td

Integrated Silicon Solution, Inc. — www.issi.com 11

Rev. A

05/02/2016

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet IS46LD32160A.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| IS46LD32160A | 512Mb Mobile LPDDR2 S4 SDRAM | ISSI |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |